# ADH8066 Quad band GSM/GPRS Module

Hardware Application Note <V1.6>

ADH Technology Co.,LTD Subject to changes in technology, design and availability URL: <u>http://www.adh-tech.com.tw</u>

## **Change History**

| Version | Effective Date | Description of Changes                       |

|---------|----------------|----------------------------------------------|

| V1.0    | 2009/8/7       | Released                                     |

| V1.1    | 2009/12/11     | Update standby power consumption             |

| V1.2    | 2010/6/25      | Add ONKEY & DSR circuit recommendation       |

| V1.3    | 2010/8/30      | Modify PWR ON/OFF sequence                   |

| V1.5    | 2010/8/30      | Correct pin 26~30 input power                |

| V1.4    | 2010/9/23      | Modify the reference schematic of Microphone |

| V 1.4   | 2010/9/23      | Input in page 13                             |

| V1.5    | 2011/06/28     | Modify PWR ON/OFF sequence                   |

| V1.6    | 2012/1/12      | Amend typo in figure 17&18                   |

### **Table of Contents**

| <u>TABI</u>                                                                              | LE OF CONTENTS                                                                                                                                   | 3                                                                                                                                              |  |

|------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|--|

| <u>LIST</u>                                                                              | OF TABLES                                                                                                                                        | 4                                                                                                                                              |  |

| <u>LIST</u>                                                                              | OF FIGURES                                                                                                                                       | 4                                                                                                                                              |  |

| ADH                                                                                      | 8066 KEY FEATURES                                                                                                                                | 5                                                                                                                                              |  |

| <u>SYST</u>                                                                              | EM ARCHITECTURE                                                                                                                                  | 6                                                                                                                                              |  |

| <u>POW</u>                                                                               | VER SUPPLY RECOMMENDATIONS                                                                                                                       | 7                                                                                                                                              |  |

| <b>3.1</b><br><b>3.2</b><br><b>3.3</b><br><b>3.4</b><br>3.4.1<br>3.4.2<br>3.4.3<br>3.4.3 | Power ON & reset circuit recommendation                                                                                                          | 7<br>7<br>7<br>8<br>8<br>8<br>8<br>9<br>9<br>9                                                                                                 |  |

| <u>INTE</u>                                                                              | RFACES                                                                                                                                           | 11                                                                                                                                             |  |

| 4.1<br>4.1.2<br>4.2<br>4.2.1<br>4.2.2<br>4.3<br>4.3.1<br>4.3.2<br>4.3.3<br>4.4<br>4.5    | AUDIO INTERFACE<br>AUDIO TRACK AND PCB LAYOUT RECOMMENDATION<br>MICROPHONE INPUTS<br>SIM INTERFACE<br>SIM INTERFACE CIRCUIT DESIGN<br>SIM LAYOUT | <ul> <li>11</li> <li>12</li> <li>12</li> <li>12</li> <li>13</li> <li>14</li> <li>14</li> <li>15</li> <li>15</li> <li>16</li> <li>17</li> </ul> |  |

| <u>5. PO</u>                                                                             | OWER ON/OFF PROCEDURE                                                                                                                            | <u>18</u>                                                                                                                                      |  |

| <u>ELEC</u>                                                                              | TRICAL & ENVIRONMENTAL CHARACTERISTICS                                                                                                           | 20                                                                                                                                             |  |

| APPI                                                                                     | ENDIX 1. SUMMARY OF PIN OUT                                                                                                                      | 21                                                                                                                                             |  |

| APPI                                                                                     | ENDIX 2. BOARD TO BOARD CONNECTOR DIMENSION                                                                                                      | 23                                                                                                                                             |  |

| АРРІ                                                                                     | PPENDIX 3. ANTENNA CONNECTOR 24                                                                                                                  |                                                                                                                                                |  |

### List of Tables

| Table 1: ADH8066 key feature list                  | 5  |

|----------------------------------------------------|----|

| Table 2: UART Data configuration                   |    |

| Table 3: UART0 pin out description                 |    |

| Table 4: UART1 pin out connector                   |    |

| Table 5: Electrical characteristics                |    |

| Table 6: SIM connector pin out                     |    |

| Table 7: MIC 1 audio input electrical requirements | 20 |

| Table 8: MIC1 audio output electrical information  |    |

| Table 9: EAR 1 audio output electrical information | 20 |

| Table 10: EAR2 audio output electrical information | 20 |

| Table 11: Input power requirement                  | 20 |

| Table 12: Operation current requirement            | 20 |

|                                                    |    |

| List of Figures                                    |    |

|                                                    |    |

### List of Figures

| Figure 1: ADH8066 system function block diagram    | 6  |

|----------------------------------------------------|----|

| Figure 2: Layout principle under GSM module        | 7  |

| Figure 3: VBAT voltage drop                        | 7  |

| Figure 4: Voltage drop versus distance             | 8  |

| Figure 5: Power supply reference circuit           | 9  |

| Figure 6: Power on reference circuit               | 9  |

| Figure 7: Value of decoupling capacitors           | 10 |

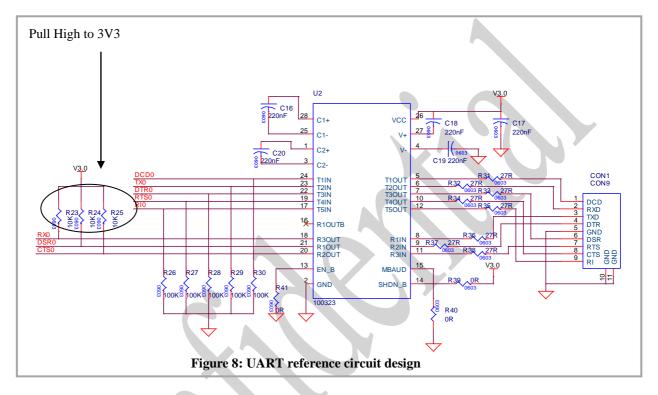

| Figure 8: UART reference circuit design            | 12 |

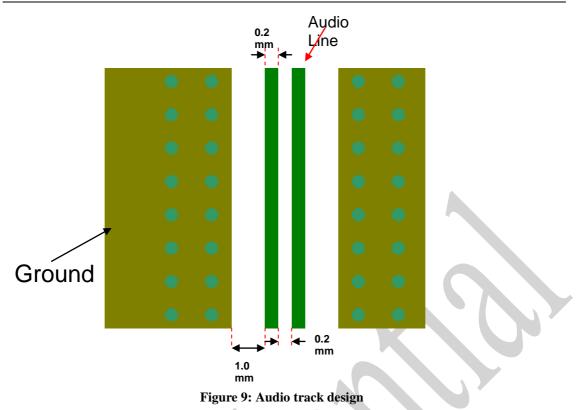

| Figure 9: Audio track design                       | 13 |

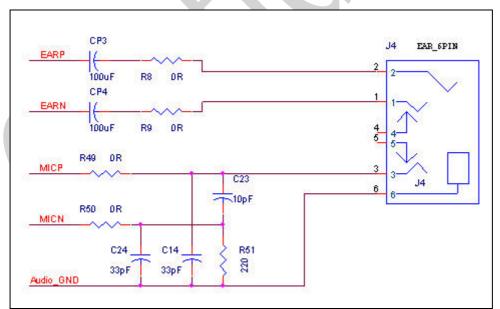

| Figure 10: Reference circuit for microphone inputs | 13 |

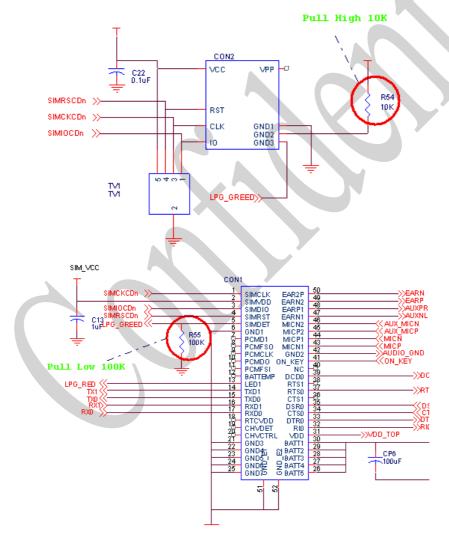

| Figure 11: Reference circuit for SIM interface     | 14 |

| Figure 12: SIM connector layout reference          | 15 |

| Figure 13: RF interface                            | 16 |

| Figure 15: PIN 13 for network ready indication     | 17 |

| Figure 14: PIN 5 for system ready indication       | 17 |

| Figure 16: Recommended ON_KEY circuit              | 18 |

| Figure 17: Power ON sequence                       | 18 |

| Figure 18: Power OFF sequence                      | 19 |

| Figure 20: 50 pin board to board connector         | 23 |

| Figure 21: RF antenna connector                    |    |

|                                                    |    |

### ADH8066 Key Features

| Table 1: ADH8060 | 6 key feature list |

|------------------|--------------------|

|------------------|--------------------|

| Product features       | Descriptions                                                                               |  |

|------------------------|--------------------------------------------------------------------------------------------|--|

| Frequency              | GSM 850/ GSM900/GSM1800 /GSM1900 Quad Band                                                 |  |

| Maximum RF Power       | GSM850/EGSM900 Class4 (2W)                                                                 |  |

|                        | GSM1800 GSM 1900 Class1 (1W)                                                               |  |

| Receiving Sensitivity  | <-106dBm                                                                                   |  |

| Working Temperature    | -30°C~+85°C                                                                                |  |

| Power Voltage          | $3.4V \sim 4.5V$ (4.0V is recommended)                                                     |  |

| Average STB current    | <2mA@paging mode 6 (Standby mode)                                                          |  |

| Leaking current        | <0.1mA                                                                                     |  |

| Protocol               | Support GSM/GPRS Phase2/2+                                                                 |  |

|                        | GSM Standard AT COMMAND                                                                    |  |

| AT COMMAND             | V.25 AT COMMAND                                                                            |  |

|                        | ADH defined AT COMMAND                                                                     |  |

| 50PIN B2B Connector    | UART Interface (Maximum I/O speed: 115200bit/s)                                            |  |

| SIM interface          | Standard SIM interface (3V/1.8V)                                                           |  |

| Audio interface        | 2 Analogue audio Input/Output interfaces                                                   |  |

| Power interface        | Power interface                                                                            |  |

| GSC RF Connector       | 50Ω                                                                                        |  |

|                        | RF Antenna Connector                                                                       |  |

| oice Communication     | Support FR, EFR, HR and AMR voice codec                                                    |  |

|                        | Support hands free operation and echo exhibition.                                          |  |

|                        | Support MO and MT                                                                          |  |

| SMS                    | Support Point-to-Point Short Message Cell Broadcast                                        |  |

| CDD C D                | Support TEXT and PDU mode                                                                  |  |

| GPRS Data transmission | GPRS CLASS 10                                                                              |  |

|                        | Coding scheme CS 1, CS 2, CS 3, CS 4                                                       |  |

|                        | Maximum transmission speed: 85.6Kbit/s <sup>-1</sup>                                       |  |

|                        | Support PBCCH                                                                              |  |

|                        | Built-in TCP/IP protocol. Support multi-slot, ACK response,                                |  |

| CSD Service            | support large memory buffer.<br>Support CSD data transmission up to 9600bit/s              |  |

| CSD Service            | Fax support: Group3, Class1.0                                                              |  |

|                        |                                                                                            |  |

| Supplemental service   | Support USSD                                                                               |  |

| Supplemental service   | Caller ID, Call transfer.<br>Support group call, broadcast, Group call service & broadcast |  |

| Group Service          | support group can, broadcast, Group can service & broadcast                                |  |

|                        |                                                                                            |  |

<sup>&</sup>lt;sup>1</sup> Depending on network condition

<sup>2</sup> Upon customer request

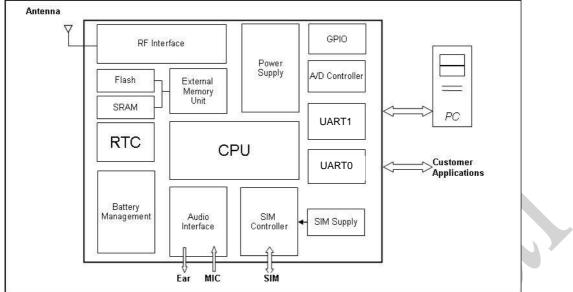

### System Architecture

Figure 1 describes ADH8066 function diagram and main system interface.

### **Power Supply Recommendations**

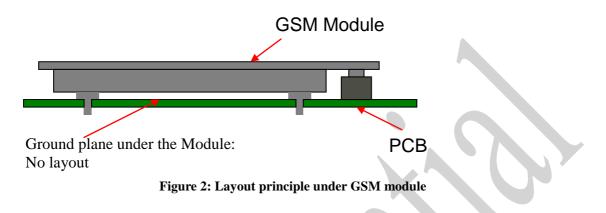

#### 3.1 Ground Connections Recommendations

The PCB right under ADH8066 should be left as a ground plane which SHOULD NOT have any components or layout circuit in case of RF interference.

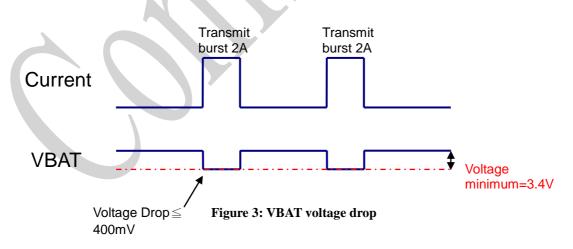

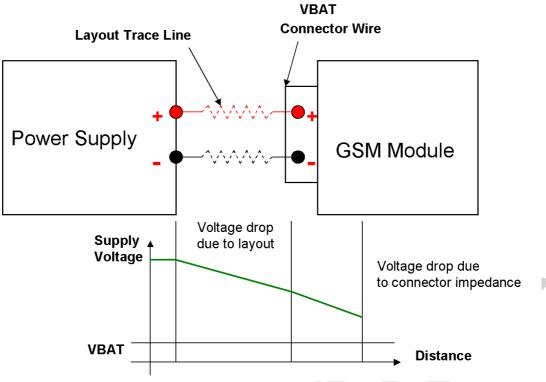

### 3.2 Power Supply Generalities

Power supply design is critical to GSM module applications. The design guides should be strictly followed to ensure the performance of the module. The VBAT voltage limits must be at any time: 3.4V <VBAT< 4.5V. The worst condition is during the burst period transmission, when current consumption is at its highest. During this period, the VBAT voltage is reduced to the lowest level:

- •The output voltage of the power supply drops.

- •Voltage drop is present between the power supply output and the GSM module supply pins (VBAT).

#### 3.3 Voltage Versus Distance

Depending on the distance between the power supply and the GSM module, behavior is described as figure 4:

Figure 4: Voltage drop versus distance

#### 3.4 Design Recommendation

Additional notes to the design of power supply circuit:

- Quality attention must be paid to the power supply circuit for their resistance value and burst current.

- The circuit line between power supply input to VBAT should try to avoid interference of other source of signals.

- Decoupling capacitors.

#### 3.4.1 Power Supply Selection

Power supply selection must fulfill following conditions:

- By using large capacity and low ESR capacitors, the system can avoid influence of over burst current.

- The power sources must have good ripple rejection. In another word, the ripple value of current input to VBAT should be as low as possible.

- Low output resistance.

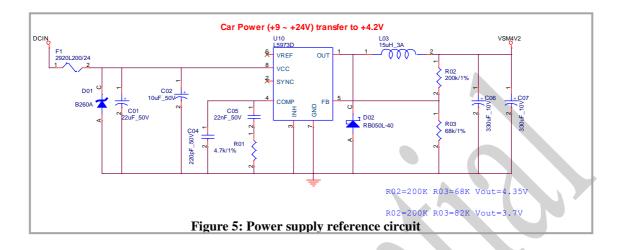

#### 3.4.2 Power Supply Circuit Recommendation

Interferences of other signal sources to the power supply must be avoided.

VBAT connection pins: Pins 26, 27, 28, 29, 30

- Track line width between the power supply and GSM VBAT input should be 3mm.

- The power circuit lines should be separated from other signal lines (e.g. Audio/SIM/UART... etc) by ground

- Makes sure to avoid having any signal lines going under the power lines.

- D01 of the input side is used to avoid over voltage of burst current to damage internal circuit. It can also avoid wrong connection of positive and negative poles.

- R02/R03 of the output side is to adjust output voltage

- Value of C06/C07 is 330uF and needs to be Low ESR capacitors.

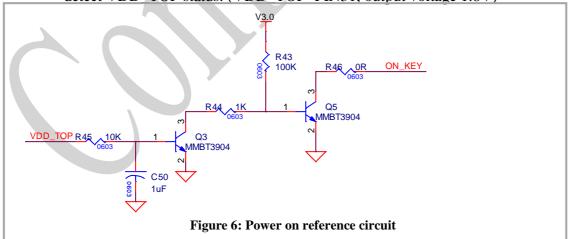

#### 3.4.3 Power ON & reset circuit recommendation

User can use ON\_KEY (PIN 41) for system reset. Pull low for 300ms to active to re-power on the system.

Power on reset recommendation circuit works as follow principles:

- 1. Before power on, VDD\_TOP=Low, ON\_KEY=Low

- 2. When the power ON, VDD\_TOP=High, ON\_KEY=High

- 3. If the system crashes then the VDD\_TOP is pulled low and ON\_KEY is pulled high automatically to reset the system by software.

- 4. VDD\_TOP is always high if system functions normally. User can use GPIO to detect VDD\_TOP status. (VDD\_TOP=PIN31, output voltage 1.8V)

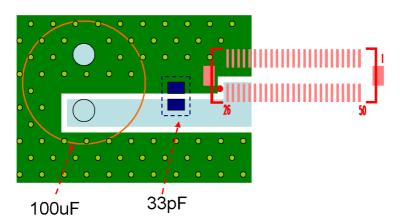

#### **3.4.4** Decoupling capacitors

The value of decoupling capacitors is 33pF/100uF, and recommended location is close to the VBAT supply pins. The purpose of these decoupling capacitors is to avoid EMI interferences.

Figure 7: Value of decoupling capacitors

### Interfaces

#### 4.1UART Interface

#### 4.1.1 UART interface characteristic and pin out description

ADH8066 has two UARTs, both are available on the bottom connector. UARTO is used to communicate with host systems, and to download the memory FLASH. The interface configuration is described as follow tables:

| Table 2: UART Dat |                |  |

|-------------------|----------------|--|

| Description       | Configurations |  |

| Baud rate         | 115,200        |  |

| Data bits         | 8 bits         |  |

| Stop bit          | 1              |  |

| Parity check      | Non            |  |

| HW flow control   | Non            |  |

| Table 3: U | Table 3: UART0 pin out description |                       |  |  |

|------------|------------------------------------|-----------------------|--|--|

| UART0      | Connector Pin                      | Description           |  |  |

| RXD0       | 17                                 | Receive Data          |  |  |

| TXD0       | 15                                 | Transmit Data         |  |  |

| DCD0       | 39                                 | Data Carrier Detected |  |  |

| DTR0       | 33                                 | Data Terminal Ready   |  |  |

| DSR0       | 35                                 | Data Set Ready        |  |  |

| RTS0       | 37                                 | Request To Send       |  |  |

| CTS0       | 34                                 | Clear to Send         |  |  |

| RI0        | 32                                 | Ring Indication       |  |  |

#### Table 4: UART1 pin out connector

| UART1 | Connector Pin | Description   |

|-------|---------------|---------------|

| RXD1  | 16            | Receive Data  |

| TXD1  | 14            | Transmit Data |

#### **Table 5: Electrical characteristics**

| ITEM | Description               | UART0 interface (UART1 for system) |                                 |

|------|---------------------------|------------------------------------|---------------------------------|

|      |                           | MIN                                | MAX                             |

| Vil  | Low level voltage input   |                                    | (0.3 x<br>VDD_IO_HIGH)<br>0.87V |

| Vih  | high level voltage input  | (0.7 x VDD_IO_HIGH)<br>2.03V       |                                 |

| Vol  | Low level voltage Output  |                                    | 0.4 V                           |

| Voh  | High level voltage output | (VDD_IO_HIGH-0.4V)<br>2.5V         |                                 |

| Iil | Low level input current   | 1 μΑ  |

|-----|---------------------------|-------|

| Iih | High level input current  | 1 μΑ  |

| Iol | Low level output current  | 4 mA  |

| Ioh | High level output current | -4 mA |

The ESD/EMI IC has internal resistors in the range of 72 W to 88W.

#### 4.1.2 UARTO interface reference circuit design

#### 4.2 Audio Interface

Two different microphone inputs and two speaker outputs are supported on ADH8066.

#### 4.2.1 Audio track and PCB Layout Recommendation

To avoid TDMA noise, it is recommended to surround the audio tracks by ground:

#### 4.2.2 Microphone Inputs

The MIC1 and MIC2 inputs already include the biasing for an electric microphone, allowing easy connection to a headset. The circuit design is as below picture. Please note that Audio\_GND (Pin42) needs to be connected to Audio Jack GND.

Figure 10: Reference circuit for microphone inputs

### 4.3 SIM Interface

ADH8066 supports 1.8V and 3.3V SIM cards. SIM\_VCC can be connected to 1.8V or 3.3V power source.

#### 4.3.1 SIM interface circuit design

ADH8066 has with SIM holder without SIM holder version. If you chose to use ADH8066 without SIM holder, please pay attention to place two capacitors in the circuit design described as follows:

- 1.  $10\mu$ F: close to the GSM module connector;

- 2. 100nF: close to the SIM connector.

These two capacitors are to avoid EMC problems. In addition, PESDXL4UW/TVSX4 connected to SIM track is to avoid ESD problem.

To implement SIM detection function, a resistor is required to add to the trace of PIN5. You need to select a SIM holder with the detection pin.

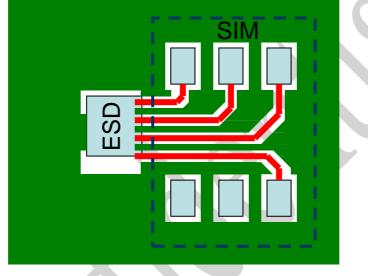

Figure 11: Reference circuit for SIM interface

#### 4.3.2 SIM Layout

It's important to pay additional caution to the ESD component of SIM connector layout. Following are suggested guidelines for the layout of SIM holder.

- 1. The ESD component should be placed as close as possible to the SIM connector.

- 2. The ESD component should be connected to a clean ground to perform well.

- 3. Track between ESD to SIM connector should be 8mil wide.

- 4. Each signal track of SIM circuit needs to be surrounded by ground.

- 5. Tracks distance between SIM connector and GSM module connector should be below 10 cm.

Figure 12: SIM connector layout reference

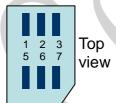

#### 4.3.3 SIM Card Interface

Table 6: SIM connector pin out

| Pin number | Schematics name | Description                |

|------------|-----------------|----------------------------|

| 1          | SIM_VCC         | Supply voltage (1.8 or 3V) |

| 2          | SIMRSCDn_ESD    | Reset for SIM card         |

| 3          | SIMCKCDn_ESD    | Clock for SIM card         |

| 5          | GND             | Ground                     |

| 6          | SIM_VCC         | Supply voltage (1.8 or 3V) |

| 7          | SIMIOCD_ESD     | I/O line to/from SIM card  |

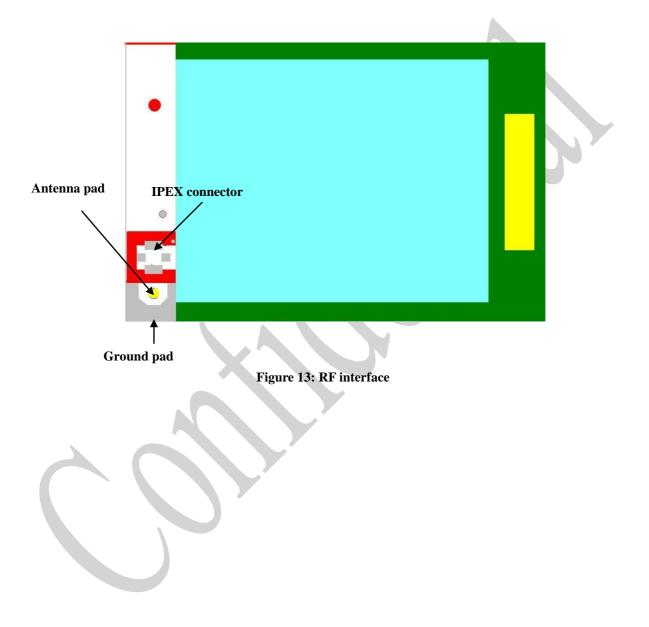

### 4.4 RF interface

When the antenna is connected to the module through a  $50\,\Omega$  coaxial cable, the coaxial cable must be connected to both the "Antenna pad" and the "Ground pad". It is recommended to use an RG178 coaxial cable with the following stripping and mounting guidelines. User needs to select RF cable with minimum signal loss at GSM 850/E-GSM 900Mhz and DCS 1800/PCS 1900Mhz.

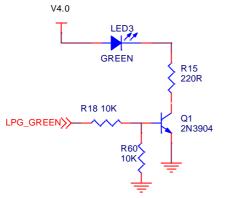

### 4.5LED Indicators

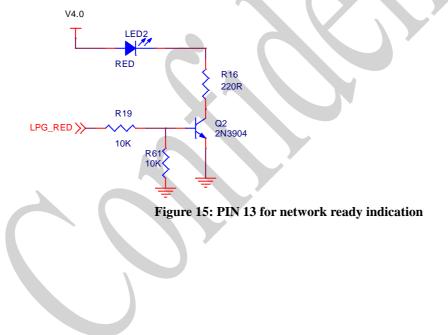

PIN 5 and PIN 13 can be used as system indicators (refer to enhanced AT command for function switch):

PIN 5: When the output is at high level, the system is ready to accept AT command.

Figure 14: PIN 5 for system ready indication

PIN 13: When the output is at high level, the module had camped on the network.

### 5. Power ON/OFF Procedure

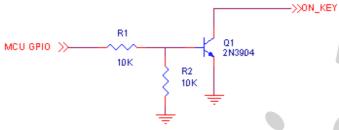

ON\_KEY: used for Power ON/OFF and this pin is active low. Please refer to the recommended circuit below.

Figure 16: Recommended ON\_KEY circuit

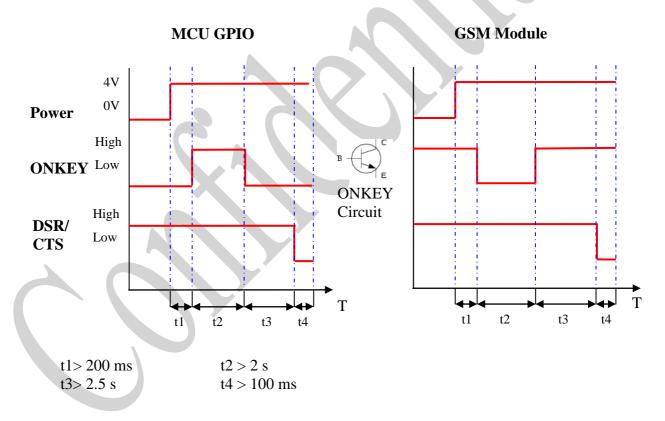

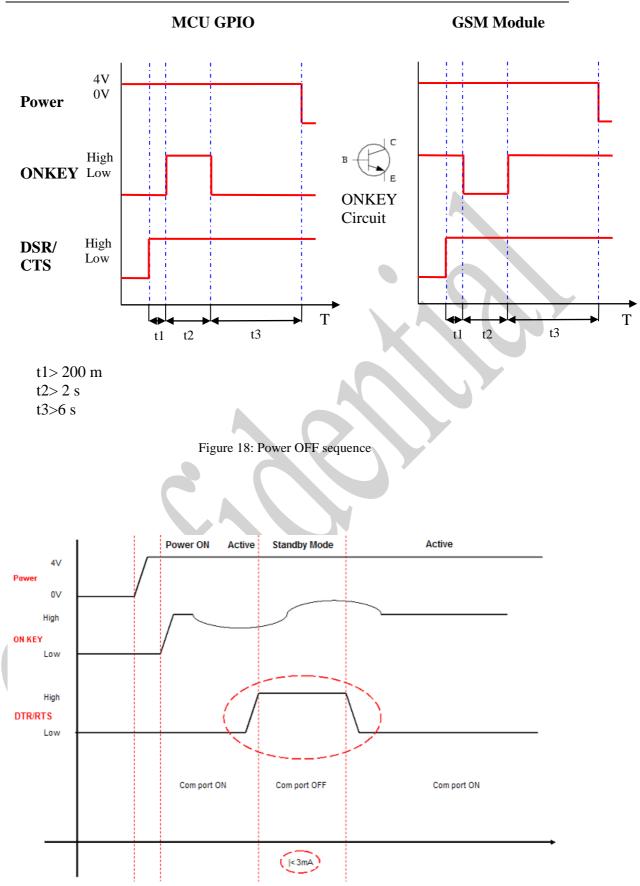

For power on and off, it is recommended to follow the procedure and time interval as shown below:

Figure 17: Power ON sequence

Figure 19: GSM Standby Process

### **Electrical & Environmental Characteristics**

| Table 7: MIC 1 audio input elec                   | ctrical require  | ments                 |        |      |             |  |

|---------------------------------------------------|------------------|-----------------------|--------|------|-------------|--|

| Parameter                                         |                  | Typical Value         |        |      |             |  |

| Maximum input level (MIC+MIC-)                    |                  | 32.5mVrms             |        |      |             |  |

| Differential input resistance (MICI+-MICI-)       |                  | 220 ΚΩ                |        |      |             |  |

| MIC Skew voltage                                  |                  | 1.9~2.1V              |        |      |             |  |

|                                                   | 2.0~2.2V         |                       |        |      |             |  |

| Table 8: MIC1 audio output ele                    | ctrical inform   | ation                 |        |      |             |  |

| Parameter                                         |                  | Testing condition     | MIN    | TYP  | MAX         |  |

| Resistance (MIC+-MIC-)                            |                  | 4VPP Output           | 16Ω    | -    | -           |  |

|                                                   |                  | 3V 1KHz               | <1Ω    | -    | -           |  |

| Table 9: EAR 1 audio output el                    | ectrical inforn  | nation                |        |      |             |  |

| Parameter                                         |                  | Testing condition     | MIN    | TYP  | MAX         |  |

| EAR+ or EAR - maximum capacitance<br>differential |                  | Differentiate<br>4VPP | K. I   |      | 1%          |  |

| EAR+ or EAR - maximum output                      |                  | 16Ω 5%                | 3.1VPP | -    | 43.92VPP    |  |

|                                                   |                  | 4Ω 5%                 | 1.2VPP | -) ( | 1.5VPP      |  |

| Table 10: EAR2 audio output el                    | lectrical inform | nation                |        |      | 1           |  |

| Parameter                                         |                  | Testing condition     | MIN    | TYP  | MAX         |  |

| EAR+ or EAR - capacitance differential            |                  | Differential 4VPP     | -      | -    | 1%          |  |

| EAR+ or EAR - maximum output                      |                  | 16Ω 5%                | 3.1VPP | -    | 43.92VPP    |  |

|                                                   |                  | 4Ω 5%                 | 1.2VPP | -    | 1.5VPP      |  |

| Table 11: Input power requiren                    |                  |                       |        |      |             |  |

| Parameter                                         | Min              | Тур                   | Max    |      | Unit        |  |

| VBat+                                             | 3.4              | 4.0                   | 4.5    | V    |             |  |

| Table 12: Operation current rec                   |                  |                       |        |      | <b>TT</b> . |  |

| Operation mode                                    | Min              | ТҮР                   | Max    |      | Unit        |  |

| Standby mode                                      | -                | -                     | 2      | mA   |             |  |

| Talking mode -                                    |                  | 250                   | -      | mA   | mA          |  |

| GPRS data transmission -                          |                  | 350(GPRS4+1)          | -      | mA   | mA          |  |

| Power off mode -                                  |                  |                       | 100    | μA   |             |  |

|                                                   |                  |                       |        | •    |             |  |

#### Table 7: MIC 1 audio input electrical requirements

### Appendix 1. Summary of Pin Out

The board to board connection pin definitions of ADH8066 are described as below table:

| PIN.NO | PIN.NAME | Note                                                                                           |  |  |  |

|--------|----------|------------------------------------------------------------------------------------------------|--|--|--|

| 1      | SIMCLK   |                                                                                                |  |  |  |

| 2      | SIMVDD   |                                                                                                |  |  |  |

| 3      | SIMIO    | SIM Card interface, supporting 1.8V/3V SIM card                                                |  |  |  |

| 4      | SIMRST   |                                                                                                |  |  |  |

| 5      | GPIO10   | Default as ready for AT COMMAND, can be used as SIM detector                                   |  |  |  |

| 6      | GND      | Ground                                                                                         |  |  |  |

| 7      | PCMDI    | PCM data input                                                                                 |  |  |  |

| 8      | PCMFSO   | PCM frame synchronization                                                                      |  |  |  |

| 9      | PCMCLK   | PCM clk                                                                                        |  |  |  |

| 10     | PCMDO    | PCM data output                                                                                |  |  |  |

| 11     | ADC1     | Adc1                                                                                           |  |  |  |

| 12     | BATTEMP  | Adc2 (bat temp)                                                                                |  |  |  |

| 13     | GPIO3    | Default as GSM network indicator                                                               |  |  |  |

| 14     | TXD1     | UART1 Data Output                                                                              |  |  |  |

| 15     | TXD0     | UART0 Data Output                                                                              |  |  |  |

| 16     | RXD1     | UART1 Data Input                                                                               |  |  |  |

| 17     | RXD0     | UART0 Data Input                                                                               |  |  |  |

| 18     | VCHAGE   | Charging interrupt detection, also can be used as charging pin with current limit under 400Ma. |  |  |  |

| 19     | VCHAGE   | Charging interrupt detection, also can be used as charging pin with current limit under 400Ma. |  |  |  |

| 20     | CHV_DRV  | CHV_DRV charging control                                                                       |  |  |  |

| 21     | GND      |                                                                                                |  |  |  |

| 22     | GND      |                                                                                                |  |  |  |

| 23     | GND      | Ground                                                                                         |  |  |  |

| 24     | GND      |                                                                                                |  |  |  |

| 25     | GND      |                                                                                                |  |  |  |

| 26     | VBAT     |                                                                                                |  |  |  |

| 27     | VBAT     |                                                                                                |  |  |  |

| 28     | VBAT     | Power input positive, input voltage is limited to 3.4V~4.5V.                                   |  |  |  |

| 29     | VBAT     |                                                                                                |  |  |  |

| 30     | VBAT     |                                                                                                |  |  |  |

| 31     | V1.8     | 1.8V Power output with load of 50mA                                                            |  |  |  |

| 32     | RIO      | UART0 ring tone indicator output, can also be used as GPIO or interrupt.                       |  |  |  |

| 33     | DTR0     | UART0 Ready to receive, can be used as GPIO                                                    |  |  |  |

| 34     | CTS0     | UART0 Permission to sent                                                                       |  |  |  |

| 35 | DSR0    | UART0 Ready to receive, can be used as GPIO or interrupt                   |  |  |

|----|---------|----------------------------------------------------------------------------|--|--|

| 36 | IICSCL  | NC                                                                         |  |  |

| 37 | RTS0    | UART0 Request to send (Output)                                             |  |  |

| 38 | IICSDA  | NC                                                                         |  |  |

| 39 | DCD0    | UART0                                                                      |  |  |

| 40 | CHV_MAX | NC                                                                         |  |  |

| 41 | ON_KEY  | Power On/OFF signal. Effective at low. Required 100ms above power<br>level |  |  |

| 42 | GND     |                                                                            |  |  |

| 43 | MIC1_P  | Mic 1 in positive                                                          |  |  |

| 44 | MIC1_N  | Mic 1 in negative                                                          |  |  |

| 45 | MIC2_P  | Mic 2 in positive                                                          |  |  |

| 46 | MIC2_N  | Mic 2 in negative                                                          |  |  |

| 47 | AUXOUTP | AUX out 2 positive                                                         |  |  |

| 48 | AUXOUTN | AUX out 2 negative                                                         |  |  |

| 49 | EARP    | Audio out 1 positive                                                       |  |  |

| 50 | EARN    | Audio out 1 negative                                                       |  |  |

### Appendix 2. Board to Board connector dimension

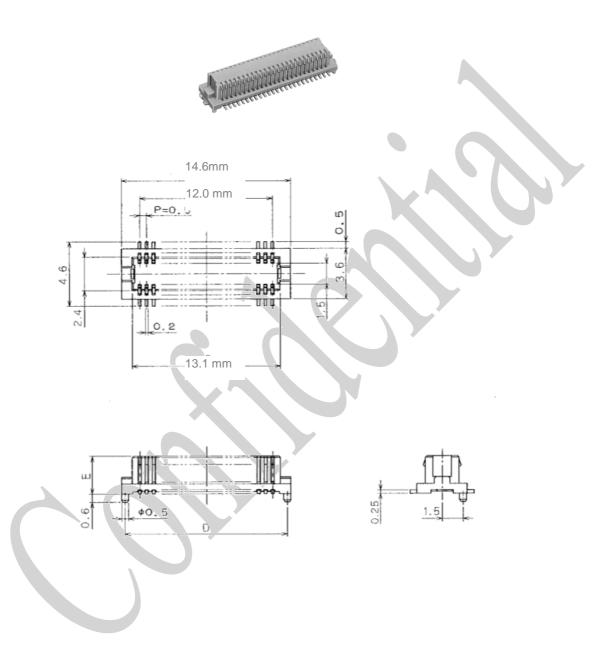

ADH8066 connector is a 50 Pin Board to Board connector with 0.5mm pitch as pig 2-1. The model number is Hirose's DF12C(3.0)-50DS-0.5V. The connector is as figure 14.

Figure 19: 50 pin board to board connector

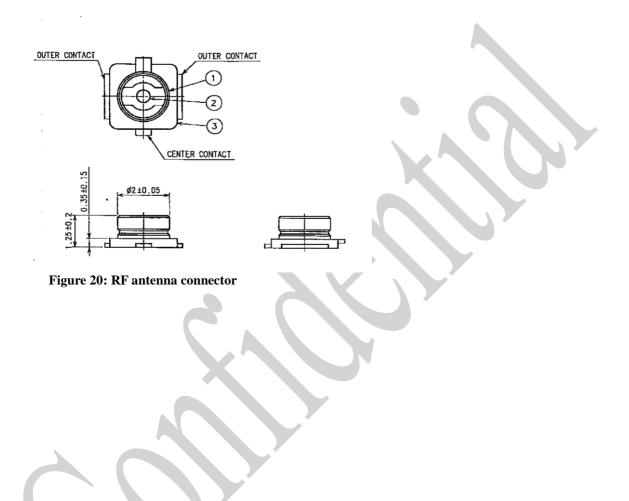

### **Appendix 3. Antenna Connector**

Antenna interface of ADH8066 is GSC RF connector to be connected with an external antenna cable to the module. ADH8066 uses an ultra-miniature SMT antenna (Model Name: U.FL-R-SMT) connector from Hirose Ltd. The physical dimension of antenna connector is described in below figure.