Application note

## LSM6DSV16X: 6-axis IMU with embedded sensor fusion, AI, Qvar for high-end applications

## Introduction

This document provides usage information and application hints related to ST's LSM6DSV16X iNEMO 6-axis IMU (inertial measurement unit).

The LSM6DSV16X is a 3-axis digital accelerometer and 3-axis digital gyroscope system-in-package with a digital I<sup>2</sup>C, SPI, and MIPI I3C<sup>®</sup> serial interface standard output, performing at 0.65 mA in combination high-performance mode. Thanks to the ultralow noise performance of both the gyroscope and the accelerometer, the device combines always-on low-power features with superior sensing precision for an optimal motion experience for the consumer. Furthermore, the accelerometer features smart sleep-to-wake-up (activity) and return-to-sleep (inactivity) functions that allow advanced power saving.

The device has a dynamic user-selectable full-scale acceleration range of  $\pm 2/\pm 4/\pm 8/\pm 16$  g and an angular rate range of  $\pm 125/\pm 250/\pm 500/\pm 1000/\pm 2000/\pm 4000$  dps. It features the capability to enable up to three different cores for UI, EIS and OIS data processing.

The LSM6DSV16X can be configured to generate interrupt signals by using hardware recognition of free-fall events, 6D orientation, tap and double-tap sensing, activity or inactivity, and wake-up events.

The availability of different connection modes to external sensors allows implementing additional functionalities such as a sensor hub, auxiliary SPI, and analog hub.

The LSM6DSV16X is compatible with the requirements of the leading OSs, offering real, virtual, and batch-mode sensors. It has been designed to implement in hardware significant motion, relative tilt, pedometer functions, timestamp, and provides an incredible level of customization: up to 8 embedded finite state machines can be programmed independently for motion detection or gesture recognition such as glance, absolute wrist tilt, shake, double-shake, or pick-up.

The LSM6DSV16X also embeds machine learning core logic which allows identifying if a data pattern matches a user-defined set of classes. A typical example of an application could be activity detection like running, walking, driving, and so on.

The LSM6DSV16X embeds an analog hub sensing functionality which is able to connect an analog input and convert it to a digital signal for embedded processing. In addition, an embedded Qvar (electric charge variation detection) channel can be used for human presence and motion detection, touch detection, and user-interface (UI) applications.

The LSM6DSV16X has an integrated smart first-in first-out (FIFO) buffer of up to 4.5 KB size, allowing dynamic batching of significant data (that is, external sensors, step counter, timestamp and temperature, MLC exported filters and features).

The LSM6DSV16X is available in a small plastic land grid array package (LGA-14L) and it is guaranteed to operate over an extended temperature range from -40 °C to +85 °C.

The ultrasmall size and weight of the SMD package make it an ideal choice for handheld portable applications such as smartphones, IoT connected devices, and wearables or any other application where reduced package size and weight are required.

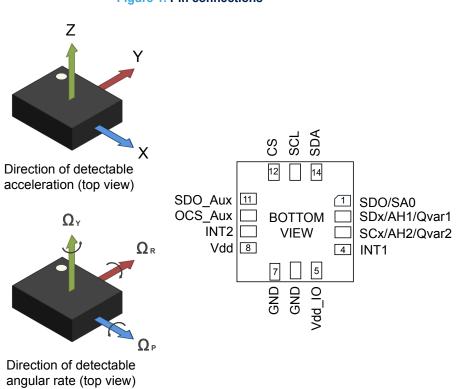

## 1 Pin description

## Table 1. Internal pin status

| pin# | Name              | Mode 1 function                                                                                                                                                                                                                                                                             | Mode 2 function                                                                                                                 | Mode 3 function                                                                                                                                                                          | Pin status mode 1                                                                                             | Pin status mode 2                                                                                             | Pin status mode 3 <sup>(1)</sup>                                                                                                                                         |

|------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | SDO               | SPI 4-wire interface serial data<br>output (SDO)                                                                                                                                                                                                                                            | SPI 4-wire interface serial data<br>output (SDO)                                                                                | SPI 4-wire interface serial data<br>output (SDO)                                                                                                                                         | Default: input without pull-up                                                                                | Default: input without pull-up                                                                                | Default: input without pull-up                                                                                                                                           |

| 1    | SA0               | I <sup>2</sup> C least significant bit of the device address (SA0)                                                                                                                                                                                                                          | I <sup>2</sup> C least significant bit of the device address (SA0)                                                              | I <sup>2</sup> C least significant bit of the device address (SA0)                                                                                                                       | Pull-up is enabled if bit<br>SDO_PU_EN = 1 in register                                                        | Pull-up is enabled if bit<br>SDO_PU_EN = 1 in register                                                        | Pull-up is enabled if bit<br>SDO_PU_EN = 1 in register                                                                                                                   |

|      | 540               | MIPI I3C <sup>®</sup> least significant bit of the static address (SA0)                                                                                                                                                                                                                     | MIPI I3C <sup>®</sup> least significant bit of the static address (SA0)                                                         | MIPI I3C <sup>®</sup> least significant bit of the static address (SA0)                                                                                                                  | PIN_CTRL (02h).                                                                                               | PIN_CTRL (02h).                                                                                               | PIN_CTRL (02h).                                                                                                                                                          |

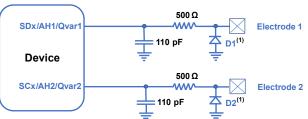

| 2    | SDx/AH1/<br>Qvar1 | Connect to Vdd_IO or GND if<br>the analog hub and/or Qvar are<br>disabled.<br>Connect to the analog input or<br>Qvar electrode 1 if the Qvar<br>function is enabled. <sup>(2)</sup>                                                                                                         | I <sup>2</sup> C serial data master (MSDA)                                                                                      | Auxiliary SPI 3/4-wire interface<br>serial data input (SDI_Aux) and<br>SPI 3-wire serial data output<br>(SDO_Aux)                                                                        | Default: input without pull-up<br>Pull-up is enabled if bit<br>SHUB_PU_EN = 1 in register<br>IF_CFG (03h).    | Default: input without pull-up<br>Pull-up is enabled if bit<br>SHUB_PU_EN = 1 in register<br>IF_CFG (03h).    | Default: input without pull-up<br>Pull-up is enabled if bit<br>SHUB_PU_EN = 1 in register<br>IF_CFG (03h).                                                               |

| 3    | SCx/AH2/<br>Qvar2 | Connect to Vdd_IO or GND if<br>the analog hub and/or Qvar are<br>disabled.<br>Connect to the analog input or<br>Qvar electrode 2 if the Qvar<br>function is enabled. <sup>(2)</sup>                                                                                                         | I <sup>2</sup> C serial clock master (MSCL)                                                                                     | Auxiliary SPI 3/4-wire interface<br>serial port clock (SPC_Aux)                                                                                                                          | Default: input without pull-up<br>Pull-up is enabled if bit<br>SHUB_PU_EN = 1 in register<br>IF_CFG (03h).    | Default: input without pull-up<br>Pull-up is enabled if bit<br>SHUB_PU_EN = 1 in register<br>IF_CFG (03h).    | Default: input without pull-up<br>Pull-up is enabled if bit<br>SHUB_PU_EN = 1 in register<br>IF_CFG (03h).                                                               |

| 4    | INT1              | Programmable interrupt 1                                                                                                                                                                                                                                                                    | Programmable interrupt 1                                                                                                        | Programmable interrupt 1                                                                                                                                                                 | Default: output forced to ground                                                                              | Default: output forced to ground                                                                              | Default: output forced to ground                                                                                                                                         |

| 5    | Vdd_IO            | Power supply for I/O pins                                                                                                                                                                                                                                                                   | Power supply for I/O pins                                                                                                       | Power supply for I/O pins                                                                                                                                                                |                                                                                                               |                                                                                                               |                                                                                                                                                                          |

| 6    | GND               | 0 V supply                                                                                                                                                                                                                                                                                  | 0 V supply                                                                                                                      | 0 V supply                                                                                                                                                                               |                                                                                                               |                                                                                                               |                                                                                                                                                                          |

| 7    | GND               | 0 V supply                                                                                                                                                                                                                                                                                  | 0 V supply                                                                                                                      | 0 V supply                                                                                                                                                                               |                                                                                                               |                                                                                                               |                                                                                                                                                                          |

| 8    | Vdd               | Power supply                                                                                                                                                                                                                                                                                | Power supply                                                                                                                    | Power supply                                                                                                                                                                             |                                                                                                               |                                                                                                               |                                                                                                                                                                          |

| 9    | INT2              | Programmable interrupt 2<br>(INT2) / Data enabled (DEN)                                                                                                                                                                                                                                     | Programmable interrupt 2<br>(INT2) / Data enabled<br>(DEN) / I <sup>2</sup> C master external<br>synchronization signal (MDRDY) | Programmable interrupt 2<br>(INT2) / Data enabled (DEN)                                                                                                                                  | Default: output forced to ground                                                                              | Default: output forced to ground                                                                              | Default: output forced to ground                                                                                                                                         |

| 10   | OCS_Aux           | Connect to Vdd_IO or<br>leave unconnected                                                                                                                                                                                                                                                   | Connect to Vdd_IO or<br>leave unconnected                                                                                       | Auxiliary SPI 3/4-wire interface<br>enabled                                                                                                                                              | Default: input with pull-up<br>Pull-up is disabled if bit<br>OIS_PU_DIS = 1 in register<br>PIN_CTRL (02h).    | Default: input with pull-up<br>Pull-up is disabled if bit<br>OIS_PU_DIS = 1 in register<br>PIN_CTRL (02h).    | Default: input without pull-up<br>(regardless of the value of<br>bit OIS_PU_DIS in register<br>PIN_CTRL (02h))                                                           |

| 11   | SDO_Aux           | Connect to Vdd_IO or<br>leave unconnected                                                                                                                                                                                                                                                   | Connect to Vdd_IO or<br>leave unconnected                                                                                       | Auxiliary SPI 3-wire interface:<br>leave unconnected / Auxiliary<br>SPI 4-wire interface: serial data<br>output (SDO_Aux)                                                                | Default: input with pull-up<br>Pull-up is disabled if bit<br>OIS_PU_DIS = 1 in register<br>PIN_CTRL (02h).    | Default: input with pull-up<br>Pull-up is disabled if bit<br>OIS_PU_DIS = 1 in register<br>PIN_CTRL (02h).    | Default: input without pull-up<br>Pull-up is enabled if bit<br>SIM_OIS = 1 (Aux_SPI 3-<br>wire) in register 70h and bit<br>OIS_PU_DIS = 0 in register<br>PIN_CTRL (02h). |

| 12   | CS                | I²C / SPI mode selection         I²C / SPI mode selection           (1: SPI idle mode / I²C<br>communication enabled;         (1: SPI idle mode / I²C<br>communication enabled;           0: SPI communication mode /<br>I²C disabled)         0: SPI communication mode /<br>I²C disabled) |                                                                                                                                 | <ul> <li>I<sup>2</sup>C / SPI mode selection</li> <li>(1: SPI idle mode / I<sup>2</sup>C communication enabled;</li> <li>0: SPI communication mode / I<sup>2</sup>C disabled)</li> </ul> | Default: input with pull-up<br>Pull-up is disabled if bit<br>I2C_I3C_disable = 1 in register<br>IF_CFG (03h). | Default: input with pull-up<br>Pull-up is disabled if bit<br>I2C_I3C_disable = 1 in register<br>IF_CFG (03h). | Default: input with pull-up<br>Pull-up is disabled if bit<br>I2C_I3C_disable = 1 in register<br>IF_CFG (03h).                                                            |

| <b>M</b> |

|----------|

|          |

| •        |

| pin# | Name | Mode 1 function                                                                                                                               | Mode 2 function Mode 3 function                                                                                                               |                                                                                                                                              | Pin status mode 1                                                                                         | Pin status mode 2                                                                                         | Pin status mode 3 <sup>(1)</sup>                                                                          |

|------|------|-----------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|

| 13   | SCL  | I <sup>2</sup> C / MIPI I3C <sup>®</sup> serial clock<br>(SCL) / SPI serial port clock<br>(SPC)                                               | I <sup>2</sup> C / MIPI I3C <sup>®</sup> serial clock<br>(SCL) / SPI serial port clock<br>(SPC)                                               | I <sup>2</sup> C / MIPI I3C <sup>®</sup> serial clock<br>(SCL) / SPI serial port clock<br>(SPC)                                              | Default: input without pull-up                                                                            | Default: input without pull-up                                                                            | Default: input without pull-up                                                                            |

| 14   | SDA  | I <sup>2</sup> C / MIPI I3C <sup>®</sup> serial data<br>(SDA) / SPI serial data input<br>(SDI) / 3-wire interface serial<br>data output (SDO) | I <sup>2</sup> C / MIPI I3C <sup>®</sup> serial data<br>(SDA) / SPI serial data input<br>(SDI) / 3-wire interface serial<br>data output (SDO) | I <sup>2</sup> C/ MIPI I3C <sup>®</sup> serial data<br>(SDA) / SPI serial data input<br>(SDI) / 3-wire interface serial<br>data output (SDO) | Default: input without pull-up<br>Pull-up is enabled if bit<br>SDA_PU_EN = 1 in register<br>IF_CFG (03h). | Default: input without pull-up<br>Pull-up is enabled if bit<br>SDA_PU_EN = 1 in register<br>IF_CFG (03h). | Default: input without pull-up<br>Pull-up is enabled if bit<br>SDA_PU_EN = 1 in register<br>IF_CFG (03h). |

1. Mode 3 is enabled when the OIS\_XL\_EN bit or the OIS\_G\_EN bit in the UI\_CTRL1\_OIS (70h) / SPI2\_CTRL1\_OIS (70h) registers is set to 1.

2. The analog hub and Qvar functions are enabled by setting the AH\_QVAR\_EN bit to 1 in CTRL7 (16h).

Internal pull-up value is from 30 k $\Omega$  to 50 k $\Omega$ , depending on Vdd\_IO.

All the registers given in the following table are accessible from the primary SPI/I<sup>2</sup>C/MIPI I3C<sup>®</sup> interface only.

| Register name    | Address | Bit7                    | Bit6                   | Bit5                   | Bit4                | Bit3                | Bit2                | Bit1                | Bit0                        |

|------------------|---------|-------------------------|------------------------|------------------------|---------------------|---------------------|---------------------|---------------------|-----------------------------|

| FUNC_CFG_ACCESS  | 01h     | EMB_FUNC_<br>REG_ACCESS | SHUB_REG<br>_ACCESS    | 0                      | 0                   | FSM_WR_<br>CTRL_EN  | SW_POR              | SPI2_RESET          | OIS_CTRL<br>_FROM_UI        |

| PIN_CTRL         | 02h     | OIS_PU_DIS              | SDO_PU_EN              | IBHR_<br>POR_EN        | 0                   | 0                   | 0                   | 1                   | 1                           |

| IF_CFG           | 03h     | SDA_PU_EN               | SHUB_PU_EN             | ASF_CTRL               | H_LACTIVE           | PP_OD               | SIM                 | 0                   | I2C_I3C_<br>disable         |

| ODR_TRIG_CFG     | 06h     | ODR_TRIG_<br>NODR_7     | ODR_TRIG_<br>NODR_6    | ODR_TRIG_<br>NODR_5    | ODR_TRIG_<br>NODR_4 | ODR_TRIG_<br>NODR_3 | ODR_TRIG_<br>NODR_2 | ODR_TRIG_<br>NODR_1 | ODR_TRIG_<br>NODR_0         |

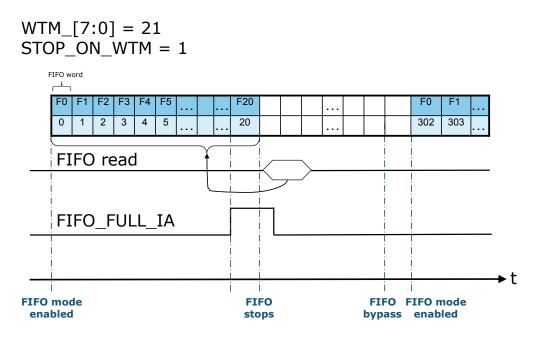

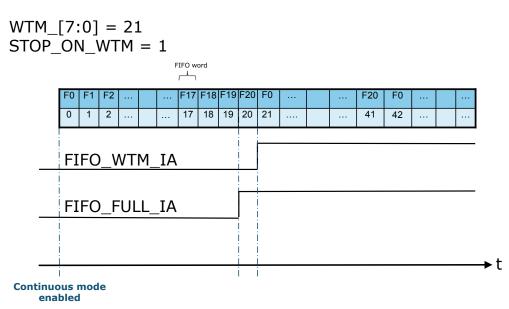

| FIFO_CTRL1       | 07h     | WTM_7                   | WTM_6                  | WTM_5                  | WTM_4               | WTM_3               | WTM_2               | WTM_1               | WTM_0                       |

| FIFO_CTRL2       | 08h     | STOP_ON_WTM             | FIFO_COMPR_<br>RT_EN   | 0                      | ODR_CHG_EN          | 0                   | UNCOMPR_<br>RATE_1  | UNCOMPR_<br>RATE_0  | XL_DualC_BATCH<br>_FROM_FSM |

| FIFO_CTRL3       | 09h     | BDR_GY_3                | BDR_GY_2               | BDR_GY_1               | BDR_GY_0            | BDR_XL_3            | BDR_XL_2            | BDR_XL_1            | BDR_XL_0                    |

| FIFO_CTRL4       | 0Ah     | DEC_TS_BATCH_1          | DEC_TS_BATCH_0         | ODR_T_BATCH_1          | ODR_T_BATCH_0       | G_EIS_FIFO_EN       | FIFO_MODE_2         | FIFO_MODE_1         | FIFO_MODE_0                 |

| COUNTER_BDR_REG1 | 0Bh     | 0                       | TRIG_COUNTER<br>_BDR_1 | TRIG_COUNTER<br>_BDR_0 | 0                   | 0                   | 0                   | CNT_BDR_TH_9        | CNT_BDR_TH_8                |

| COUNTER_BDR_REG2 | 0Ch     | CNT_BDR_TH_7            | CNT_BDR_TH_6           | CNT_BDR_TH_5           | CNT_BDR_TH_4        | CNT_BDR_TH_3        | CNT_BDR_TH_2        | CNT_BDR_TH_1        | CNT_BDR_TH_0                |

| INT1_CTRL        | 0Dh     | 0                       | INT1_CNT_BDR           | INT1_FIFO_FULL         | INT1_FIFO_OVR       | INT1_FIFO_TH        | 0                   | INT1_DRDY_G         | INT1_DRDY_XL                |

| INT2_CTRL        | 0Eh     | INT2_EMB_<br>FUNC_ENDOP | INT2_CNT_BDR           | INT2_FIFO_FULL         | INT2_FIFO_OVR       | INT2_FIFO_TH        | INT2_DRDY_G_EIS     | INT2_DRDY_G         | INT2_DRDY_XL                |

| WHO_AM_I         | 0Fh     | 0                       | 1                      | 1                      | 1                   | 0                   | 0                   | 0                   | 0                           |

| CTRL1            | 10h     | 0                       | OP_MODE_XL_2           | OP_MODE_XL_1           | OP_MODE_XL_0        | ODR_XL_3            | ODR_XL_2            | ODR_XL_1            | ODR_XL_0                    |

| CTRL2            | 11h     | 0                       | OP_MODE_G_2            | OP_MODE_G_1            | OP_MODE_G_0         | ODR_G_3             | ODR_G_2             | ODR_G_1             | ODR_G_0                     |

| CTRL3            | 12h     | BOOT                    | BDU                    | 0                      | 0                   | 0                   | IF_INC              | 0                   | SW_RESET                    |

| CTRL4            | 13h     | 0                       | 0                      | 0                      | INT2_on_INT1        | DRDY_MASK           | INT2_DRDY_TEMP      | DRDY_PULSED         | INT2_IN_LH                  |

| CTRL5            | 14h     | 0                       | 0                      | 0                      | 0                   | 0                   | BUS_ACT_SEL_1       | BUS_ACT_SEL_0       | INT_EN_I3C                  |

| CTRL6            | 15h     | 0                       | LPF1_G_BW_2            | LPF1_G_BW_1            | LPF1_G_BW_0         | FS_G_3              | FS_G_2              | FS_G_1              | FS_G_0                      |

| CTRL7            | 16h     | AH_QVAR_EN              | INT2_DRDY_<br>AH_QVAR  | AH_QVAR_<br>C_ZIN_1    | AH_QVAR_<br>C_ZIN_0 | 0                   | 0                   | 0                   | LPF1_G_EN                   |

| CTRL8            | 17h     | HP_LPF2_<br>XL_BW_2     | HP_LPF2_<br>XL_BW_1    | HP_LPF2_<br>XL_BW_0    | 0                   | XL_DualC_EN         | 0                   | FS_XL_1             | FS_XL_0                     |

| CTRL9            | 18h     | 0                       | HP_REF_<br>MODE_XL     | XL_FASTSETTL_<br>MODE  | HP_SLOPE_XL_EN      | LPF2_XL_EN          | 0                   | USR_OFF_W           | USR_OFF_<br>ON_OUT          |

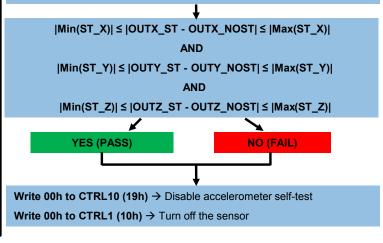

| CTRL10           | 19h     | 0                       | EMB_FUNC<br>_DEBUG     | 0                      | 0                   | ST_G_1              | ST_G_0              | ST_XL_1             | ST_XL_0                     |

| Register name         | Address | Bit7                   | Bit6        | Bit5                | Bit4           | Bit3                 | Bit2                   | Bit1        | Bit0        |

|-----------------------|---------|------------------------|-------------|---------------------|----------------|----------------------|------------------------|-------------|-------------|

| CTRL_STATUS           | 1Ah     | 0                      | 0           | 0                   | 0              | 0                    | FSM_WR_<br>CTRL_STATUS | -           | 0           |

| FIFO_STATUS1          | 1Bh     | DIFF_FIFO_7            | DIFF_FIFO_6 | DIFF_FIFO_5         | DIFF_FIFO_4    | DIFF_FIFO_3          | DIFF_FIFO_2            | DIFF_FIFO_1 | DIFF_FIFO_0 |

| FIFO_STATUS2          | 1Ch     | FIFO_WTM_IA            | FIFO_OVR_IA | FIFO_FULL_IA        | COUNTER_BDR_IA | FIFO_OVR_<br>LATCHED | 0                      | 0           | DIFF_FIFO_8 |

| ALL_INT_SRC           | 1Dh     | EMB_FUNC_IA            | SHUB_IA     | SLEEP_<br>CHANGE_IA | D6D_IA         | 0                    | TAP_IA                 | WU_IA       | FF_IA       |

| STATUS_REG            | 1Eh     | TIMESTAMP_<br>ENDCOUNT | 0           | OIS_DRDY            | GDA_EIS        | AH_QVARDA            | TDA                    | GDA         | XLDA        |

| OUT_TEMP_L            | 20h     | Temp7                  | Temp6       | Temp5               | Temp4          | Temp3                | Temp2                  | Temp1       | Temp0       |

| OUT_TEMP_H            | 21h     | Temp15                 | Temp14      | Temp13              | Temp12         | Temp11               | Temp10                 | Temp9       | Temp8       |

| OUTX_L_G              | 22h     | D7                     | D6          | D5                  | D4             | D3                   | D2                     | D1          | D0          |

| OUTX_H_G              | 23h     | D15                    | D14         | D13                 | D12            | D11                  | D10                    | D9          | D8          |

| OUTY_L_G              | 24h     | D7                     | D6          | D5                  | D4             | D3                   | D2                     | D1          | D0          |

| OUTY_H_G              | 25h     | D15                    | D14         | D13                 | D12            | D11                  | D10                    | D9          | D8          |

| OUTZ_L_G              | 26h     | D7                     | D6          | D5                  | D4             | D3                   | D2                     | D1          | D0          |

| OUTZ_H_G              | 27h     | D15                    | D14         | D13                 | D12            | D11                  | D10                    | D9          | D8          |

| OUTX_L_A              | 28h     | D7                     | D6          | D5                  | D4             | D3                   | D2                     | D1          | D0          |

| OUTX_H_A              | 29h     | D15                    | D14         | D13                 | D12            | D11                  | D10                    | D9          | D8          |

| OUTY_L_A              | 2Ah     | D7                     | D6          | D5                  | D4             | D3                   | D2                     | D1          | D0          |

| OUTY_H_A              | 2Bh     | D15                    | D14         | D13                 | D12            | D11                  | D10                    | D9          | D8          |

| OUTZ_L_A              | 2Ch     | D7                     | D6          | D5                  | D4             | D3                   | D2                     | D1          | D0          |

| OUTZ_H_A              | 2Dh     | D15                    | D14         | D13                 | D12            | D11                  | D10                    | D9          | D8          |

| UI_OUTX_L_G_OIS_EIS   | 2Eh     | D7                     | D6          | D5                  | D4             | D3                   | D2                     | D1          | D0          |

| UI_OUTX_H_G_OIS_EIS   | 2Fh     | D15                    | D14         | D13                 | D12            | D11                  | D10                    | D9          | D8          |

| UI_OUTY_L_G_OIS_EIS   | 30h     | D7                     | D6          | D5                  | D4             | D3                   | D2                     | D1          | D0          |

| UI_OUTY_H_G_OIS_EIS   | 31h     | D15                    | D14         | D13                 | D12            | D11                  | D10                    | D9          | D8          |

| UI_OUTZ_L_G_OIS_EIS   | 32h     | D7                     | D6          | D5                  | D4             | D3                   | D2                     | D1          | D0          |

| UI_OUTZ_H_G_OIS_EIS   | 33h     | D15                    | D14         | D13                 | D12            | D11                  | D10                    | D9          | D8          |

| UI_OUTX_L_A_OIS_DualC | 34h     | D7                     | D6          | D5                  | D4             | D3                   | D2                     | D1          | D0          |

| UI_OUTX_H_A_OIS_DualC | 35h     | D15                    | D14         | D13                 | D12            | D11                  | D10                    | D9          | D8          |

| UI_OUTY_L_A_OIS_DualC | 36h     | D7                     | D6          | D5                  | D4             | D3                   | D2                     | D1          | D0          |

| UI_OUTY_H_A_OIS_DualC | 37h     | D15                    | D14         | D13                 | D12            | D11                  | D10                    | D9          | D8          |

| UI_OUTZ_L_A_OIS_DualC | 38h     | D7                     | D6          | D5                  | D4             | D3                   | D2                     | D1          | D0          |

| UI_OUTZ_H_A_OIS_DualC | 39h     | D15                    | D14         | D13                 | D12            | D11                  | D10                    | D9          | D8          |

| AH_QVAR_OUT_L         | 3Ah     | AH_Qvar_7              | AH_Qvar_6   | AH_Qvar_5           | AH_Qvar_4      | AH_Qvar_3            | AH_Qvar_2              | AH_Qvar_1   | AH_Qvar_0   |

| AH_QVAR_OUT_H         | 3Bh     | AH_Qvar_15             | AH_Qvar_14  | AH_Qvar_13          | AH_Qvar_12     | AH_Qvar_11           | AH_Qvar_10             | AH_Qvar_9   | AH_Qvar_8   |

Register name

TIMESTAMP0

TIMESTAMP1

| TIMESTAMPT                   | 410 | DIS                        | D14                  | D13                           | DIZ                            | DII                     | DIU            | Da            | D8                 |

|------------------------------|-----|----------------------------|----------------------|-------------------------------|--------------------------------|-------------------------|----------------|---------------|--------------------|

| TIMESTAMP2                   | 42h | D23                        | D22                  | D21                           | D20                            | D19                     | D18            | D17           | D16                |

| TIMESTAMP3                   | 43h | D31                        | D30                  | D29                           | D28                            | D27                     | D26            | D25           | D24                |

| UI_STATUS_REG_OIS            | 44h | 0                          | 0                    | 0                             | 0                              | 0                       | GYRO_SETTLING  | GDA_OIS       | XLDA_OIS           |

| WAKE_UP_SRC                  | 45h | 0                          | SLEEP_<br>CHANGE_IA  | FF_IA                         | SLEEP_STATE                    | WU_IA                   | X_WU           | Y_WU          | Z_WU               |

| TAP_SRC                      | 46h | 0                          | TAP_IA               | SINGLE_TAP                    | DOUBLE_TAP                     | TAP_SIGN                | X_TAP          | Y_TAP         | Z_TAP              |

| D6D_SRC                      | 47h | 0                          | D6D_IA               | ZH                            | ZL                             | YH                      | YL             | ХН            | XL                 |

| STATUS_MASTER_<br>MAINPAGE   | 48h | WR_ONCE_DONE               | SLAVE3_NACK          | SLAVE2_NACK                   | SLAVE1_NACK                    | SLAVE0_NACK             | 0              | 0             | SENS_HUB_<br>ENDOP |

| EMB_FUNC_STATUS_<br>MAINPAGE | 49h | IS_FSM_LC                  | 0                    | IS_SIGMOT                     | IS_TILT                        | IS_STEP_DET             | 0              | 0             | 0                  |

| FSM_STATUS_MAINPAGE          | 4Ah | IS_FSM8                    | IS_FSM7              | IS_FSM6                       | IS_FSM5                        | IS_FSM4                 | IS_FSM3        | IS_FSM2       | IS_FSM1            |

| MLC_STATUS_MAINPAGE          | 4Bh | 0                          | 0                    | 0                             | 0                              | IS_MLC4                 | IS_MLC3        | IS_MLC2       | IS_MLC1            |

| INTERNAL_FREQ_FINE           | 4Fh | FREQ_FINE_7                | FREQ_FINE_6          | FREQ_FINE_5                   | FREQ_FINE_4                    | FREQ_FINE_3             | FREQ_FINE_2    | FREQ_FINE_1   | FREQ_FINE_0        |

| FUNCTIONS_ENABLE             | 50h | INTERRUPTS_<br>ENABLE      | TIMESTAMP_EN         | 0                             | 0                              | DIS_RST_LIR_<br>ALL_INT | 0              | INACT_EN_1    | INACT_EN_0         |

| DEN                          | 51h | 0                          | LVL1_EN              | LVL2_EN                       | DEN_XL_EN                      | DEN_X                   | DEN_Y          | DEN_Z         | DEN_XL_G           |

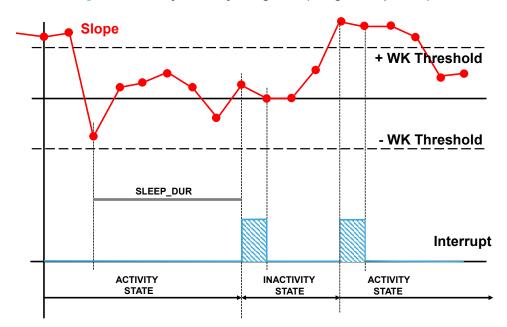

| INACTIVITY_DUR               | 54h | SLEEP_STATUS_<br>ON_INT    | WU_INACT_<br>THS_W_2 | WU_INACT_<br>THS_W_1          | WU_INACT_<br>THS_W_0           | XL_INACT_ODR_1          | XL_INACT_ODR_0 | INACT_DUR_1   | INACT_DUR_0        |

| INACTIVITY_THS               | 55h | 0                          | 0                    | INACT_THS_5                   | INACT_THS_4                    | INACT_THS_3             | INACT_THS_2    | INACT_THS_1   | INACT_THS_0        |

| TAP_CFG0                     | 56h | 0                          | LOW_PASS_<br>ON_6D   | HW_FUNC_MASK<br>_XL_SETTL     | SLOPE_FDS                      | TAP_X_EN                | TAP_Y_EN       | TAP_Z_EN      | LIR                |

| TAP_CFG1                     | 57h | TAP_PRIORITY_2             | TAP_PRIORITY_1       | TAP_PRIORITY_0                | TAP_THS_X_4                    | TAP_THS_X_3             | TAP_THS_X_2    | TAP_THS_X_1   | TAP_THS_X_0        |

| TAP_CFG2                     | 58h | 0                          | 0                    | 0                             | TAP_THS_Y_4                    | TAP_THS_Y_3             | TAP_THS_Y_2    | TAP_THS_Y_1   | TAP_THS_Y_0        |

| TAP_THS_6D                   | 59h | D4D_EN                     | SIXD_THS_1           | SIXD_THS_0                    | TAP_THS_Z_4                    | TAP_THS_Z_3             | TAP_THS_Z_2    | TAP_THS_Z_1   | TAP_THS_Z_0        |

| TAP_DUR                      | 5Ah | DUR_3                      | DUR_2                | DUR_1                         | DUR_0                          | QUIET_1                 | QUIET_0        | SHOCK_1       | SHOCK_0            |

| WAKE_UP_THS                  | 5Bh | SINGLE_<br>DOUBLE_TAP      | USR_OFF_ON_WU        | WK_THS_5                      | WK_THS_4                       | WK_THS_3                | WK_THS_2       | WK_THS_1      | WK_THS_0           |

| WAKE_UP_DUR                  | 5Ch | FF_DUR_5                   | WAKE_DUR_1           | WAKE_DUR_0                    | 0                              | SLEEP_DUR_3             | SLEEP_DUR_2    | SLEEP_DUR_1   | SLEEP_DUR_0        |

| FREE_FALL                    | 5Dh | FF_DUR_4                   | FF_DUR_3             | FF_DUR_2                      | FF_DUR_1                       | FF_DUR_0                | FF_THS_2       | FF_THS_1      | FF_THS_0           |

| MD1_CFG                      | 5Eh | INT1_SLEEP<br>_CHANGE      | INT1_<br>SINGLE_TAP  | INT1_WU                       | INT1_FF                        | INT1_<br>DOUBLE_TAP     | INT1_6D        | INT1_EMB_FUNC | INT1_SHUB          |

| MD2_CFG                      | 5Fh | INT2_SLEEP<br>_CHANGE      | INT2_<br>SINGLE_TAP  | INT2_WU                       | INT2_FF                        | INT2_<br>DOUBLE_TAP     | INT2_6D        | INT2_EMB_FUNC | INT2_TIMESTAMP     |

| HAODR_CFG                    | 62h | 0                          | 0                    | 0                             | 0                              | 0                       | 0              | HAODR_SEL_1   | HAODR_SEL_0        |

| EMB_FUNC_CFG                 | 63h | XL_DualC_BATCH<br>_FROM_IF | 0                    | EMB_FUNC_IRQ<br>_MASK_G_SETTL | EMB_FUNC_IRQ_<br>MASK_XL_SETTL | EMB_FUNC_<br>DISABLE    | 0              | 0             | 0                  |

| UI_HANDSHAKE_CTRL            | 64h | 0                          | 0                    | 0                             | 0                              | 0                       | 0              | UI_SHARED_ACK | UI_SHARED_REQ      |

Bit7

D7

D15

Address

40h

41h

Bit6

D6

D14

Bit5

D5

D13

Bit4

D4

D12

Bit3

D3

D11

Bit2

D2

D10

Bit1

D1

D9

Bit0

D0

D8

| Register name     | Address | Bit7          | Bit6          | Bit5                | Bit4                | Bit3                       | Bit2        | Bit1        | Bit0         |

|-------------------|---------|---------------|---------------|---------------------|---------------------|----------------------------|-------------|-------------|--------------|

| UI_SPI2_SHARED_0  | 65h     | D7            | D6            | D5                  | D4                  | D3                         | D2          | D1          | D0           |

| UI_SPI2_SHARED_1  | 66h     | D7            | D6            | D5                  | D4                  | D3                         | D2          | D1          | D0           |

| UI_SPI2_SHARED_2  | 67h     | D7            | D6            | D5                  | D4                  | D3                         | D2          | D1          | D0           |

| UI_SPI2_SHARED_3  | 68h     | D7            | D6            | D5                  | D4                  | D3                         | D2          | D1          | D0           |

| UI_SPI2_SHARED_4  | 69h     | D7            | D6            | D5                  | D4                  | D3                         | D2          | D1          | D0           |

| UI_SPI2_SHARED_5  | 6Ah     | D7            | D6            | D5                  | D4                  | D3                         | D2          | D1          | D0           |

| CTRL_EIS          | 6Bh     | ODR_G_EIS_1   | ODR_G_EIS_0   | 0                   | LPF_G_EIS_BW        | G_EIS_ON_G_<br>OIS_OUT_REG | FS_G_EIS_2  | FS_G_EIS_1  | FS_G_EIS_0   |

| UI_INT_OIS        | 6Fh     | INT2_DRDY_OIS | DRDY_MASK_OIS | 0                   | ST_OIS_<br>CLAMPDIS | 0                          | 0           | 0           | 0            |

| UI_CTRL1_OIS      | 70h     | 0             | 0             | SIM_OIS             | 0                   | 0                          | OIS_XL_EN   | OIS_G_EN    | SPI2_READ_EN |

| UI_CTRL2_OIS      | 71h     | 0             | 0             | 0                   | LPF1_G_OIS<br>_BW_1 | LPF1_G_OIS<br>_BW_0        | FS_G_OIS_2  | FS_G_OIS_1  | FS_G_OIS_0   |

| UI_CTRL3_OIS      | 72h     | 0             | 0             | LPF_XL_OIS<br>_BW_2 | LPF_XL_OIS<br>_BW_1 | LPF_XL_OIS<br>_BW_0        | 0           | FS_XL_OIS_1 | FS_XL_OIS_0  |

| X_OFS_USR         | 73h     | X_OFS_USR_7   | X_OFS_USR_6   | X_OFS_USR_5         | X_OFS_USR_4         | X_OFS_USR_3                | X_OFS_USR_2 | X_OFS_USR_1 | X_OFS_USR_0  |

| Y_OFS_USR         | 74h     | Y_OFS_USR_7   | Y_OFS_USR_6   | Y_OFS_USR_5         | Y_OFS_USR_4         | Y_OFS_USR_3                | Y_OFS_USR_2 | Y_OFS_USR_1 | Y_OFS_USR_0  |

| Z_OFS_USR         | 75h     | Z_OFS_USR_7   | Z_OFS_USR_6   | Z_OFS_USR_5         | Z_OFS_USR_4         | Z_OFS_USR_3                | Z_OFS_USR_2 | Z_OFS_USR_1 | Z_OFS_USR_0  |

| FIFO_DATA_OUT_TAG | 78h     | TAG_SENSOR_4  | TAG_SENSOR_3  | TAG_SENSOR_2        | TAG_SENSOR_1        | TAG_SENSOR_0               | TAG_CNT_1   | TAG_CNT_0   | -            |

| FIFO_DATA_OUT_X_L | 79h     | D7            | D6            | D5                  | D4                  | D3                         | D2          | D1          | D0           |

| FIFO_DATA_OUT_X_H | 7Ah     | D15           | D14           | D13                 | D12                 | D11                        | D10         | D9          | D8           |

| FIFO_DATA_OUT_Y_L | 7Bh     | D7            | D6            | D5                  | D4                  | D3                         | D2          | D1          | D0           |

| FIFO_DATA_OUT_Y_H | 7Ch     | D15           | D14           | D13                 | D12                 | D11                        | D10         | D9          | D8           |

| FIFO_DATA_OUT_Z_L | 7Dh     | D7            | D6            | D5                  | D4                  | D3                         | D2          | D1          | D0           |

| FIFO_DATA_OUT_Z_H | 7Eh     | D15           | D14           | D13                 | D12                 | D11                        | D10         | D9          | D8           |

All the registers given in the following table are accessible from the auxiliary SPI interface only.

# AN5763 - Re

| Register name       | Address | Bit7          | Bit6          | Bit5                | Bit4                | Bit3                | Bit2          | Bit1                | Bit0                |

|---------------------|---------|---------------|---------------|---------------------|---------------------|---------------------|---------------|---------------------|---------------------|

| SPI2_WHO_AM_I       | 0Fh     | 0             | 1             | 1                   | 1                   | 0                   | 0             | 0                   | 0                   |

| SPI2_STATUS_REG_OIS | 1Eh     | 0             | 0             | 0                   | 0                   | 0                   | GYRO_SETTLING | GDA                 | XLDA                |

| SPI2_OUT_TEMP_L     | 20h     | Temp7         | Temp6         | Temp5               | Temp4               | Temp3               | Temp2         | Temp1               | Temp0               |

| SPI2_OUT_TEMP_H     | 21h     | Temp15        | Temp14        | Temp13              | Temp12              | Temp11              | Temp10        | Temp9               | Temp8               |

| SPI2_OUTX_L_G_OIS   | 22h     | D7            | D6            | D5                  | D4                  | D3                  | D2            | D1                  | D0                  |

| SPI2_OUTX_H_G_OIS   | 23h     | D15           | D14           | D13                 | D12                 | D11                 | D10           | D9                  | D8                  |

| SPI2_OUTY_L_G_OIS   | 24h     | D7            | D6            | D5                  | D4                  | D3                  | D2            | D1                  | D0                  |

| SPI2_OUTY_H_G_OIS   | 25h     | D15           | D14           | D13                 | D12                 | D11                 | D10           | D9                  | D8                  |

| SPI2_OUTZ_L_G_OIS   | 26h     | D7            | D6            | D5                  | D4                  | D3                  | D2            | D1                  | D0                  |

| SPI2_OUTZ_H_G_OIS   | 27h     | D15           | D14           | D13                 | D12                 | D11                 | D10           | D9                  | D8                  |

| SPI2_OUTX_L_A_OIS   | 28h     | D7            | D6            | D5                  | D4                  | D3                  | D2            | D1                  | D0                  |

| SPI2_OUTX_H_A_OIS   | 29h     | D15           | D14           | D13                 | D12                 | D11                 | D10           | D9                  | D8                  |

| SPI2_OUTY_L_A_OIS   | 2Ah     | D7            | D6            | D5                  | D4                  | D3                  | D2            | D1                  | D0                  |

| SPI2_OUTY_H_A_OIS   | 2Bh     | D15           | D14           | D13                 | D12                 | D11                 | D10           | D9                  | D8                  |

| SPI2_OUTZ_L_A_OIS   | 2Ch     | D7            | D6            | D5                  | D4                  | D3                  | D2            | D1                  | D0                  |

| SPI2_OUTZ_H_A_OIS   | 2Dh     | D15           | D14           | D13                 | D12                 | D11                 | D10           | D9                  | D8                  |

| SPI2_HANDSHAKE_CTRL | 6Eh     | 0             | 0             | 0                   | 0                   | 0                   | 0             | SPI2_<br>SHARED_REQ | SPI2_<br>SHARED_ACK |

| SPI2_INT_OIS        | 6Fh     | INT2_DRDY_OIS | DRDY_MASK_OIS | 0                   | ST_OIS_<br>CLAMPDIS | ST_G_OIS_1          | ST_G_OIS_0    | ST_XL_OIS_1         | ST_XL_OIS_0         |

| SPI2_CTRL1_OIS      | 70h     | 0             | 0             | SIM_OIS             | 0                   | 0                   | OIS_XL_EN     | OIS_G_EN            | SPI2_READ_EN        |

| SPI2_CTRL2_OIS      | 71h     | 0             | 0             | 0                   | LPF1_G_<br>OIS_BW_1 | LPF1_G_<br>OIS_BW_0 | FS_G_OIS_2    | FS_G_OIS_1          | FS_G_OIS_0          |

| SPI2_CTRL3_OIS      | 72h     | 0             | 0             | LPF_XL_<br>OIS_BW_2 | LPF_XL_<br>OIS_BW_1 | LPF_XL_<br>OIS_BW_0 | 0             | FS_XL_OIS_1         | FS_XL_OIS_0         |

## 2.1 Embedded functions registers

The table given below provides a list of the registers for the embedded functions available in the device and the corresponding addresses. Embedded functions registers are accessible when the EMB\_FUNC\_REG\_ACCESS bit is set to 1 in the FUNC\_CFG\_ACCESS register.

| Register name            | Address | Bit7                  | Bit6                     | Bit5                   | Bit4                     | Bit3                   | Bit2        | Bit1                           | Bit0               |

|--------------------------|---------|-----------------------|--------------------------|------------------------|--------------------------|------------------------|-------------|--------------------------------|--------------------|

| PAGE_SEL                 | 02h     | PAGE_SEL3             | PAGE_SEL2                | PAGE_SEL1              | PAGE_SEL0                | 0                      | 0           | 0                              | 1                  |

| EMB_FUNC_EN_A            | 04h     | MLC_BEFORE<br>_FSM_EN | 0                        | SIGN_MOTION_EN         | TILT_EN                  | PEDO_EN                | 0           | SFLP_GAME_EN                   | 0                  |

| EMB_FUNC_EN_B            | 05h     | 0                     | 0                        | 0                      | MLC_EN                   | FIFO_COMPR_EN          | 0           | 0                              | FSM_EN             |

| EMB_FUNC_EXEC_STAT<br>US | 07h     | 0                     | 0                        | 0                      | 0                        | 0                      | 0           | EMB_FUNC_<br>EXEC_OVR          | EMB_FUNC<br>_ENDOP |

| PAGE_ADDRESS             | 08h     | PAGE_ADDR7            | PAGE_ADDR6               | PAGE_ADDR5             | PAGE_ADDR4               | PAGE_ADDR3             | PAGE_ADDR2  | PAGE_ADDR1                     | PAGE_ADDR0         |

| PAGE_VALUE               | 09h     | PAGE_VALUE7           | PAGE_VALUE6              | PAGE_VALUE5            | PAGE_VALUE4              | PAGE_VALUE3            | PAGE_VALUE2 | PAGE_VALUE1                    | PAGE_VALUE0        |

| EMB_FUNC_INT1            | 0Ah     | INT1_FSM_LC           | 0                        | INT1_SIG_MOT           | INT1_TILT                | INT1_STEP_<br>DETECTOR | 0           | 0                              | 0                  |

| FSM_INT1                 | 0Bh     | INT1_FSM8             | INT1_FSM7                | INT1_FSM6              | INT1_FSM5                | INT1_FSM4              | INT1_FSM3   | INT1_FSM2                      | INT1_FSM1          |

| MLC_INT1                 | 0Dh     | 0                     | 0                        | 0                      | 0                        | INT1_MLC4              | INT1_MLC3   | INT1_MLC2                      | INT1_MLC1          |

| EMB_FUNC_INT2            | 0Eh     | INT2_FSM_LC           | 0                        | INT2_SIG_MOT           | INT2_TILT                | INT2_STEP_<br>DETECTOR | 0           | 0                              | 0                  |

| FSM_INT2                 | 0Fh     | INT2_FSM8             | INT2_FSM7                | INT2_FSM6              | INT2_FSM5                | INT2_FSM4              | INT2_FSM3   | INT2_FSM2                      | INT2_FSM1          |

| MLC_INT2                 | 11h     | 0                     | 0                        | 0                      | 0                        | INT2_MLC4              | INT2_MLC3   | INT2_MLC2                      | INT2_MLC1          |

| EMB_FUNC_STATUS          | 12h     | IS_FSM_LC             | 0                        | IS_SIGMOT              | IS_TILT                  | IS_STEP_DET            | 0           | 0                              | 0                  |

| FSM_STATUS               | 13h     | IS_FSM8               | IS_FSM7                  | IS_FSM6                | IS_FSM5                  | IS_FSM4                | IS_FSM3     | IS_FSM2                        | IS_FSM1            |

| MLC_STATUS               | 15h     | 0                     | 0                        | 0                      | 0                        | IS_MLC4                | IS_MLC3     | IS_MLC2                        | IS_MLC1            |

| PAGE_RW                  | 17h     | EMB_FUNC_LIR          | PAGE_WRITE               | PAGE_READ              | 0                        | 0                      | 0           | 0                              | 0                  |

| EMB_FUNC_FIFO_EN_A       | 44h     | MLC_FIFO_EN           | STEP_COUNTER<br>_FIFO_EN | SFLP_GBIAS<br>_FIFO_EN | SFLP_GRAVITY<br>_FIFO_EN | 0                      | 0           | SFLP_GAME<br>_FIFO_EN          | 0                  |

| EMB_FUNC_FIFO_EN_B       | 45h     | 0                     | 0                        | 0                      | 0                        | 0                      | 0           | MLC_FILTER_<br>FEATURE_FIFO_EN | 0                  |

| FSM_ENABLE               | 46h     | FSM8_EN               | FSM7_EN                  | FSM6_EN                | FSM5_EN                  | FSM4_EN                | FSM3_EN     | FSM2_EN                        | FSM1_EN            |

| FSM_LONG_COUNTER_L       | 48h     | FSM_LC_7              | FSM_LC_6                 | FSM_LC_5               | FSM_LC_4                 | FSM_LC_3               | FSM_LC_2    | FSM_LC_1                       | FSM_LC_0           |

| FSM_LONG_COUNTER_H       | 49h     | FSM_LC_15             | FSM_LC_14                | FSM_LC_13              | FSM_LC_12                | FSM_LC_11              | FSM_LC_10   | FSM_LC_9                       | FSM_LC_8           |

| INT_ACK_MASK             | 4Bh     | IACK_MASK7            | IACK_MASK6               | IACK_MASK5             | IACK_MASK4               | IACK_MASK3             | IACK_MASK2  | IACK_MASK1                     | IACK_MASK0         |

| FSM_OUTS1                | 4Ch     | P_X                   | N_X                      | P_Y                    | N_Y                      | P_Z                    | N_Z         | P_V                            | N_V                |

| FSM_OUTS2                | 4Dh     | P_X                   | N_X                      | P_Y                    | N_Y                      | P_Z                    | N_Z         | P_V                            | N_V                |

| FSM_OUTS3                | 4Eh     | P_X                   | N_X                      | P_Y                    | N_Y                      | P_Z                    | N_Z         | P_V                            | N_V                |

| FSM_OUTS4                | 4Fh     | P_X                   | N_X                      | P_Y                    | N_Y                      | P_Z                    | N_Z         | P_V                            | N_V                |

| FSM_OUTS5                | 50h     | P_X                   | N_X                      | P_Y                    | N_Y                      | P_Z                    | N_Z         | P_V                            | N_V                |

#### Table 4. Embedded functions registers

| Register name   | Address | Bit7                    | Bit6       | Bit5                | Bit4                    | Bit3                | Bit2                    | Bit1               | Bit0       |

|-----------------|---------|-------------------------|------------|---------------------|-------------------------|---------------------|-------------------------|--------------------|------------|

| FSM_OUTS6       | 51h     | P_X                     | N_X        | P_Y                 | N_Y                     | P_Z                 | N_Z                     | P_V                | N_V        |

| FSM_OUTS7       | 52h     | P_X                     | N_X        | P_Y                 | N_Y                     | P_Z                 | N_Z                     | P_V                | N_V        |

| FSM_OUTS8       | 53h     | P_X                     | N_X        | P_Y                 | N_Y                     | P_Z                 | N_Z                     | P_V                | N_V        |

| SFLP_ODR        | 5Eh     | 0                       | 1          | SFLP_GAME<br>_ODR_2 | SFLP_GAME<br>_ODR_1     | SFLP_GAME<br>_ODR_0 | 0                       | 1                  | 1          |

| FSM_ODR         | 5Fh     | 0                       | 1          | FSM_ODR_2           | FSM_ODR_1               | FSM_ODR_0           | 0                       | 1                  | 1          |

| MLC_ODR         | 60h     | 0                       | MLC_ODR_2  | MLC_ODR_1           | MLC_ODR_0               | 0                   | 1                       | 0                  | 1          |

| STEP_COUNTER_L  | 62h     | STEP_7                  | STEP_6     | STEP_5              | STEP_4                  | STEP_3              | STEP_2                  | STEP_1             | STEP_0     |

| STEP_COUNTER_H  | 63h     | STEP_15                 | STEP_14    | STEP_13             | STEP_12                 | STEP_11             | STEP_10                 | STEP_9             | STEP_8     |

| EMB_FUNC_SRC    | 64h     | PEDO_RST_STEP           | 0          | STEP_DETECTED       | STEP_COUNT_<br>DELTA_IA | STEP_OVERFLOW       | STEPCOUNTER<br>_BIT_SET | 0                  | 0          |

| EMB_FUNC_INIT_A | 66h     | MLC_BEFORE<br>_FSM_INIT | 0          | SIG_MOT_INIT        | TILT_INIT               | STEP_DET_INIT       | 0                       | SFLP_GAME<br>_INIT | 0          |

| EMB_FUNC_INIT_B | 67h     | 0                       | 0          | 0                   | MLC_INIT                | FIFO_COMPR<br>_INIT | 0                       | 0                  | FSM_INIT   |

| MLC1_SRC        | 70h     | MLC1_SRC_7              | MLC1_SRC_6 | MLC1_SRC_5          | MLC1_SRC_4              | MLC1_SRC_3          | MLC1_SRC_2              | MLC1_SRC_1         | MLC1_SRC_0 |

| MLC2_SRC        | 71h     | MLC2_SRC_7              | MLC2_SRC_6 | MLC2_SRC_5          | MLC2_SRC_4              | MLC2_SRC_3          | MLC2_SRC_2              | MLC2_SRC_1         | MLC2_SRC_0 |

| MLC3_SRC        | 72h     | MLC3_SRC_7              | MLC3_SRC_6 | MLC3_SRC_5          | MLC3_SRC_4              | MLC3_SRC_3          | MLC3_SRC_2              | MLC3_SRC_1         | MLC3_SRC_0 |

| MLC4_SRC        | 73h     | MLC4_SRC_7              | MLC4_SRC_6 | MLC4_SRC_5          | MLC4_SRC_4              | MLC4_SRC_3          | MLC4_SRC_2              | MLC4_SRC_1         | MLC4_SRC_0 |

## 2.2 Embedded advanced features pages

The table given below provides a list of the registers for the embedded advanced features page 0. These registers are accessible when PAGE\_SEL[3:0] are set to 0000 in the PAGE\_SEL register.

| Register name         | Address | Bit7              | Bit6              | Bit5              | Bit4              | Bit3              | Bit2              | Bit1             | Bit0             |

|-----------------------|---------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| SFLP_GAME_GBIASX_L    | 6Eh     | GAME_GBIASX_7     | GAME_GBIASX_6     | GAME_GBIASX_5     | GAME_GBIASX_4     | GAME_GBIASX_3     | GAME_GBIASX_2     | GAME_GBIASX_1    | GAME_GBIASX_0    |

| SFLP_GAME_GBIASX_H    | 6Fh     | GAME_GBIASX_15    | GAME_GBIASX_14    | GAME_GBIASX_13    | GAME_GBIASX_12    | GAME_GBIASX_11    | GAME_GBIASX_10    | GAME_GBIASX_9    | GAME_GBIASX_8    |

| SFLP_GAME_GBIASY_L    | 70h     | GAME_GBIASY_7     | GAME_GBIASY_6     | GAME_GBIASY_5     | GAME_GBIASY_4     | GAME_GBIASY_3     | GAME_GBIASY_2     | GAME_GBIASY_1    | GAME_GBIASY_0    |

| SFLP_GAME_GBIASY_H    | 71h     | GAME_GBIASY_15    | GAME_GBIASY_14    | GAME_GBIASY_13    | GAME_GBIASY_12    | GAME_GBIASY_11    | GAME_GBIASY_10    | GAME_GBIASY_9    | GAME_GBIASY_8    |

| SFLP_GAME_GBIASZ_L    | 72h     | GAME_GBIASZ_7     | GAME_GBIASZ_6     | GAME_GBIASZ_5     | GAME_GBIASZ_4     | GAME_GBIASZ_3     | GAME_GBIASZ_2     | GAME_GBIASZ_1    | GAME_GBIASZ_0    |

| SFLP_GAME_GBIASZ_H    | 73h     | GAME_GBIASZ_15    | GAME_GBIASZ_14    | GAME_GBIASZ_13    | GAME_GBIASZ_12    | GAME_GBIASZ_11    | GAME_GBIASZ_10    | GAME_GBIASZ_9    | GAME_GBIASZ_8    |

| FSM_EXT_SENSITIVITY_L | BAh     | FSM_EXT_S_7       | FSM_EXT_S_6       | FSM_EXT_S_5       | FSM_EXT_S_4       | FSM_EXT_S_3       | FSM_EXT_S_2       | FSM_EXT_S_1      | FSM_EXT_S_0      |

| FSM_EXT_SENSITIVITY_H | BBh     | FSM_EXT_S_15      | FSM_EXT_S_14      | FSM_EXT_S_13      | FSM_EXT_S_12      | FSM_EXT_S_11      | FSM_EXT_S_10      | FSM_EXT_S_9      | FSM_EXT_S_8      |

| FSM_EXT_OFFX_L        | C0h     | FSM_EXT_OFFX_7    | FSM_EXT_OFFX_6    | FSM_EXT_OFFX_5    | FSM_EXT_OFFX_4    | FSM_EXT_OFFX_3    | FSM_EXT_OFFX_2    | FSM_EXT_OFFX_1   | FSM_EXT_OFFX_0   |

| FSM_EXT_OFFX_H        | C1h     | FSM_EXT_OFFX_15   | FSM_EXT_OFFX_14   | FSM_EXT_OFFX_13   | FSM_EXT_OFFX_12   | FSM_EXT_OFFX_11   | FSM_EXT_OFFX_10   | FSM_EXT_OFFX_9   | FSM_EXT_OFFX_8   |

| FSM_EXT_OFFY_L        | C2h     | FSM_EXT_OFFY_7    | FSM_EXT_OFFY_6    | FSM_EXT_OFFY_5    | FSM_EXT_OFFY_4    | FSM_EXT_OFFY_3    | FSM_EXT_OFFY_2    | FSM_EXT_OFFY_1   | FSM_EXT_OFFY_0   |

| FSM_EXT_OFFY_H        | C3h     | FSM_EXT_OFFY_15   | FSM_EXT_OFFY_14   | FSM_EXT_OFFY_13   | FSM_EXT_OFFY_12   | FSM_EXT_OFFY_11   | FSM_EXT_OFFY_10   | FSM_EXT_OFFY_9   | FSM_EXT_OFFY_8   |

| FSM_EXT_OFFZ_L        | C4h     | FSM_EXT_OFFZ_7    | FSM_EXT_OFFZ_6    | FSM_EXT_OFFZ_5    | FSM_EXT_OFFZ_4    | FSM_EXT_OFFZ_3    | FSM_EXT_OFFZ_2    | FSM_EXT_OFFZ_1   | FSM_EXT_OFFZ_0   |

| FSM_EXT_OFFZ_H        | C5h     | FSM_EXT_OFFZ_15   | FSM_EXT_OFFZ_14   | FSM_EXT_OFFZ_13   | FSM_EXT_OFFZ_12   | FSM_EXT_OFFZ_11   | FSM_EXT_OFFZ_10   | FSM_EXT_OFFZ_9   | FSM_EXT_OFFZ_8   |

| FSM_EXT_MATRIX_XX_L   | C6h     | FSM_EXT_MAT_XX_7  | FSM_EXT_MAT_XX_6  | FSM_EXT_MAT_XX_5  | FSM_EXT_MAT_XX_4  | FSM_EXT_MAT_XX_3  | FSM_EXT_MAT_XX_2  | FSM_EXT_MAT_XX_1 | FSM_EXT_MAT_XX_  |

| FSM_EXT_MATRIX_XX_H   | C7h     | FSM_EXT_MAT_XX_15 | FSM_EXT_MAT_XX_14 | FSM_EXT_MAT_XX_13 | FSM_EXT_MAT_XX_12 | FSM_EXT_MAT_XX_11 | FSM_EXT_MAT_XX_10 | FSM_EXT_MAT_XX_9 | FSM_EXT_MAT_XX_  |

| FSM_EXT_MATRIX_XY_L   | C8h     | FSM_EXT_MAT_XY_7  | FSM_EXT_MAT_XY_6  | FSM_EXT_MAT_XY_5  | FSM_EXT_MAT_XY_4  | FSM_EXT_MAT_XY_3  | FSM_EXT_MAT_XY_2  | FSM_EXT_MAT_XY_1 | FSM_EXT_MATXY_0  |

| FSM_EXT_MATRIX_XY_H   | C9h     | FSM_EXT_MAT_XY_15 | FSM_EXT_MAT_XY_14 | FSM_EXT_MAT_XY_13 | FSM_EXT_MAT_XY_12 | FSM_EXT_MAT_XY_11 | FSM_EXT_MAT_XY_10 | FSM_EXT_MAT_XY_9 | FSM_EXT_MAT_XY_  |

| FSM_EXT_MATRIX_XZ_L   | CAh     | FSM_EXT_MAT_XZ_7  | FSM_EXT_MAT_XZ_6  | FSM_EXT_MAT_XZ_5  | FSM_EXT_MAT_XZ_4  | FSM_EXT_MAT_XZ_3  | MAG_SI_XZ_2       | FSM_EXT_MAT_XZ_1 | FSM_EXT_MAT_XZ_  |

| FSM_EXT_MATRIX_XZ_H   | CBh     | FSM_EXT_MAT_XZ_15 | FSM_EXT_MAT_XZ_14 | FSM_EXT_MAT_XZ_13 | FSM_EXT_MAT_XZ_12 | FSM_EXT_MAT_XZ_11 | FSM_EXT_MAT_XZ_10 | FSM_EXT_MAT_XZ_9 | FSM_EXT_MAT_XZ_8 |

| FSM_EXT_MATRIX_YY_L   | CCh     | FSM_EXT_MAT_YY_7  | FSM_EXT_MAT_YY_6  | FSM_EXT_MAT_YY_5  | FSM_EXT_MAT_YY_4  | FSM_EXT_MAT_YY_3  | FSM_EXT_MAT_YY_2  | FSM_EXT_MAT_YY_1 | FSM_EXT_MAT_YY_  |

| FSM_EXT_MATRIX_YY_H   | CDh     | FSM_EXT_MAT_YY_15 | FSM_EXT_MAT_YY_14 | FSM_EXT_MAT_YY_13 | FSM_EXT_MAT_YY_12 | FSM_EXT_MAT_YY_11 | FSM_EXT_MAT_YY_10 | FSM_EXT_MAT_YY_9 | FSM_EXT_MAT_YY_  |

| FSM_EXT_MATRIX_YZ_L   | CEh     | FSM_EXT_MAT_YZ_7  | FSM_EXT_MAT_YZ_6  | FSM_EXT_MAT_YZ_5  | FSM_EXT_MAT_YZ_4  | FSM_EXT_MAT_YZ_3  | FSM_EXT_MAT_YZ_2  | FSM_EXT_MAT_YZ_1 | FSM_EXT_MAT_YZ_  |

| FSM_EXT_MATRIX_YZ_H   | CFh     | FSM_EXT_MAT_YZ_15 | FSM_EXT_MAT_YZ_14 | FSM_EXT_MAT_YZ_13 | FSM_EXT_MAT_YZ_12 | FSM_EXT_MAT_YZ_11 | FSM_EXT_MAT_YZ_10 | FSM_EXT_MAT_YZ_9 | FSM_EXT_MAT_YZ_  |

| FSM_EXT_MATRIX_ZZ_L   | D0h     | FSM_EXT_MAT_ZZ_7  | FSM_EXT_MAT_ZZ_6  | FSM_EXT_MAT_ZZ_5  | FSM_EXT_MAT_ZZ_4  | FSM_EXT_MAT_ZZ_3  | FSM_EXT_MAT_ZZ_2  | FSM_EXT_MAT_ZZ_1 | FSM_EXT_MAT_ZZ_  |

| FSM_EXT_MATRIX_ZZ_H   | D1h     | FSM_EXT_MAT_ZZ_15 | FSM_EXT_MAT_ZZ_14 | FSM_EXT_MAT_ZZ_13 | FSM_EXT_MAT_ZZ_12 | FSM_EXT_MAT_ZZ_11 | FSM_EXT_MAT_ZZ_10 | FSM_EXT_MAT_ZZ_9 | FSM_EXT_MAT_ZZ_  |

| EXT_CFG_A             | D4h     | 0                 | EXT_Y_AXIS2       | EXT_Y_AXIS1       | EXT_Y_AXIS0       | 0                 | EXT_Z_AXIS2       | EXT_Z_AXIS1      | EXT_Z_AXIS0      |

| EXT_CFG_B             | D5h     | 0                 | 0                 | 0                 | 0                 | 0                 | EXT_X_AXIS2       | EXT_X_AXIS1      | EXT_X_AXIS0      |

| Register name         | Address | Bit7                 | Bit6                 | Bit5                 | Bit4                 | Bit3                 | Bit2                 | Bit1                | Bit0                |

|-----------------------|---------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|---------------------|---------------------|

| FSM_LC_TIMEOUT_L      | 7Ah     | FSM_LC_<br>TIMEOUT7  | FSM_LC_<br>TIMEOUT6  | FSM_LC_<br>TIMEOUT5  | FSM_LC_<br>TIMEOUT4  | FSM_LC_<br>TIMEOUT3  | FSM_LC_<br>TIMEOUT2  | FSM_LC_<br>TIMEOUT1 | FSM_LC_<br>TIMEOUT0 |

| FSM_LC_TIMEOUT_H      | 7Bh     | FSM_LC_<br>TIMEOUT15 | FSM_LC_<br>TIMEOUT14 | FSM_LC_<br>TIMEOUT13 | FSM_LC_<br>TIMEOUT12 | FSM_LC_<br>TIMEOUT11 | FSM_LC_<br>TIMEOUT10 | FSM_LC_<br>TIMEOUT9 | FSM_LC_<br>TIMEOUT8 |

| FSM_PROGRAMS          | 7Ch     | FSM_N_PROG7          | FSM_N_PROG6          | FSM_N_PROG5          | FSM_N_PROG4          | FSM_N_PROG3          | FSM_N_PROG2          | FSM_N_PROG1         | FSM_N_PROG0         |

| FSM_START_ADD_L       | 7Eh     | FSM_START7           | FSM_START6           | FSM_START5           | FSM_START4           | FSM_START3           | FSM_START2           | FSM_START1          | FSM_START0          |

| FSM_START_ADD_H       | 7Fh     | FSM_START15          | FSM_START714         | FSM_START13          | FSM_START12          | FSM_START11          | FSM_START10          | FSM_START9          | FSM_START8          |

| PEDO_CMD_REG          | 83h     | 0                    | 0                    | 0                    | 0                    | CARRY_<br>COUNT_EN   | FP_<br>REJECTION_EN  | 0                   | 0                   |

| PEDO_DEB_STEPS_CONF   | 84h     | DEB_STEP7            | DEB_STEP6            | DEB_STEP5            | DEB_STEP4            | DEB_STEP3            | DEB_STEP2            | DEB_STEP1           | DEB_STEP0           |

| PEDO_SC_DELTAT_L      | D0h     | PD_SC_7              | PD_SC_6              | PD_SC_5              | PD_SC_4              | PD_SC_3              | PD_SC_2              | PD_SC_1             | PD_SC_0             |

| PEDO_SC_DELTAT_H      | D1h     | PD_SC_15             | PD_SC_14             | PD_SC_13             | PD_SC_12             | PD_SC_11             | PD_SC_10             | PD_SC_9             | PD_SC_8             |

| MLC_EXT_SENSITIVITY_L | E8h     | MLC_EXT_S_7          | MLC_EXT_S_6          | MLC_EXT_S_5          | MLC_EXT_S_4          | MLC_EXT_S_3          | MLC_EXT_S_2          | MLC_EXT_S_1         | MLC_EXT_S_0         |

| MLC_EXT_SENSITIVITY_H | E9h     | MLC_EXT_S_15         | MLC_EXT_S_14         | MLC_EXT_S_13         | MLC_EXT_S_12         | MLC_EXT_S_11         | MLC_EXT_S_10         | MLC_EXT_S_9         | MLC_EXT_S_8         |

#### Table 6. Embedded advanced features registers - page 1

The following table provides a list of the registers for the embedded advanced features page 2. These registers are accessible when PAGE\_SEL[3:0] are set to 0010 in the PAGE\_SEL register.

#### Table 7. Embedded advanced features registers - page 2

| Register name           | Address | Bit7             | Bit6             | Bit5             | Bit4             | Bit3             | Bit2             | Bit1             | Bit0             |

|-------------------------|---------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|

| EXT_FORMAT              | 00h     | 0                | 0                | 0                | 0                | 0                | EXT_FORMAT_SEL   | 0                | 0                |

| EXT_3BYTE_SENSITIVITY_L | 02h     | EXT_3BYTE_S_7    | EXT_3BYTE_S_6    | EXT_3BYTE_S_5    | EXT_3BYTE_S_4    | EXT_3BYTE_S_3    | EXT_3BYTE_S_2    | EXT_3BYTE_S_1    | EXT_3BYTE_S_0    |

| EXT_3BYTE_SENSITIVITY_H | 03h     | EXT_3BYTE_S_15   | EXT_3BYTE_S_14   | EXT_3BYTE_S_13   | EXT_3BYTE_S_12   | EXT_3BYTE_S_11   | EXT_3BYTE_S_10   | EXT_3BYTE_S_9    | EXT_3BYTE_S_8    |

| EXT_3BYTE_OFFSET_XL     | 06h     | EXT_3BYTE_OFF_7  | EXT_3BYTE_OFF_6  | EXT_3BYTE_OFF_5  | EXT_3BYTE_OFF_4  | EXT_3BYTE_OFF_3  | EXT_3BYTE_OFF_2  | EXT_3BYTE_OFF_1  | EXT_3BYTE_OFF_0  |

| EXT_3BYTE_OFFSET_L      | 07h     | EXT_3BYTE_OFF_15 | EXT_3BYTE_OFF_14 | EXT_3BYTE_OFF_13 | EXT_3BYTE_OFF_12 | EXT_3BYTE_OFF_11 | EXT_3BYTE_OFF_10 | EXT_3BYTE_OFF_9  | EXT_3BYTE_OFF_8  |

| EXT_3BYTE_OFFSET_H      | 08h     | EXT_3BYTE_OFF_23 | EXT_3BYTE_OFF_22 | EXT_3BYTE_OFF_21 | EXT_3BYTE_OFF_20 | EXT_3BYTE_OFF_19 | EXT_3BYTE_OFF_18 | EXT_3BYTE_OFF_17 | EXT_3BYTE_OFF_16 |

AN5763 - Rev 2

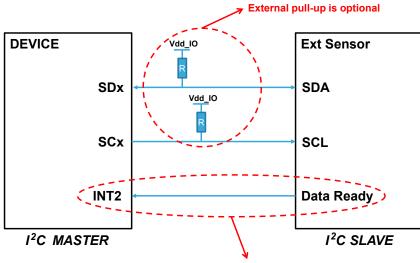

## 2.3 Sensor hub registers

The table given below provides a list of the registers for the sensor hub functions available in the device and the corresponding addresses. The sensor hub registers are accessible when bit SHUB\_REG\_ACCESS is set to 1 in the FUNC\_CFG\_ACCESS register.

| Register name | Address | Bit7                | Bit6          | Bit5          | Bit4                  | Bit3                    | Bit2          | Bit1          | Bit0          |

|---------------|---------|---------------------|---------------|---------------|-----------------------|-------------------------|---------------|---------------|---------------|

| SENSOR_HUB_1  | 02h     | SensorHub1_7        | SensorHub1_6  | SensorHub1_5  | SensorHub1_4          | SensorHub1_3            | SensorHub1_2  | SensorHub1_1  | SensorHub1_0  |

| SENSOR_HUB_2  | 03h     | SensorHub2_7        | SensorHub2_6  | SensorHub2_5  | SensorHub2_4          | SensorHub2_3            | SensorHub2_2  | SensorHub2_1  | SensorHub2_0  |

| SENSOR_HUB_3  | 04h     | SensorHub3_7        | SensorHub3_6  | SensorHub3_5  | SensorHub3_4          | SensorHub3_3            | SensorHub3_2  | SensorHub3_1  | SensorHub3_0  |

| SENSOR_HUB_4  | 05h     | SensorHub4_7        | SensorHub4_6  | SensorHub4_5  | SensorHub4_4          | SensorHub4_3            | SensorHub4_2  | SensorHub4_1  | SensorHub4_0  |

| SENSOR_HUB_5  | 06h     | SensorHub5_7        | SensorHub5_6  | SensorHub5_5  | SensorHub5_4          | SensorHub5_3            | SensorHub5_2  | SensorHub5_1  | SensorHub5_0  |

| SENSOR_HUB_6  | 07h     | SensorHub6_7        | SensorHub6_6  | SensorHub6_5  | SensorHub6_4          | SensorHub6_3            | SensorHub6_2  | SensorHub6_1  | SensorHub6_0  |

| SENSOR_HUB_7  | 08h     | SensorHub7_7        | SensorHub7_6  | SensorHub7_5  | SensorHub7_4          | SensorHub7_3            | SensorHub7_2  | SensorHub7_1  | SensorHub7_0  |

| SENSOR_HUB_8  | 09h     | SensorHub8_7        | SensorHub8_6  | SensorHub8_5  | SensorHub8_4          | SensorHub8_3            | SensorHub8_2  | SensorHub8_1  | SensorHub8_0  |

| SENSOR_HUB_9  | 0Ah     | SensorHub9_7        | SensorHub9_6  | SensorHub9_5  | SensorHub9_4          | SensorHub9_3            | SensorHub9_2  | SensorHub9_1  | SensorHub9_0  |

| SENSOR_HUB_10 | 0Bh     | SensorHub10_7       | SensorHub10_6 | SensorHub10_5 | SensorHub10_4         | SensorHub10_3           | SensorHub10_2 | SensorHub10_1 | SensorHub10_0 |

| SENSOR_HUB_11 | 0Ch     | SensorHub11_7       | SensorHub11_6 | SensorHub11_5 | SensorHub11_4         | SensorHub11_3           | SensorHub11_2 | SensorHub11_1 | SensorHub11_0 |

| SENSOR_HUB_12 | 0Dh     | SensorHub12_7       | SensorHub12_6 | SensorHub12_5 | SensorHub12_4         | SensorHub12_3           | SensorHub12_2 | SensorHub12_1 | SensorHub12_0 |

| SENSOR_HUB_13 | 0Eh     | SensorHub13_7       | SensorHub13_6 | SensorHub13_5 | SensorHub13_4         | SensorHub13_3           | SensorHub13_2 | SensorHub13_1 | SensorHub13_0 |

| SENSOR_HUB_14 | 0Fh     | SensorHub14_7       | SensorHub14_6 | SensorHub14_5 | SensorHub14_4         | SensorHub14_3           | SensorHub14_2 | SensorHub14_1 | SensorHub14_0 |

| SENSOR_HUB_15 | 10h     | SensorHub15_7       | SensorHub15_6 | SensorHub15_5 | SensorHub15_4         | SensorHub15_3           | SensorHub15_2 | SensorHub15_1 | SensorHub15_0 |

| SENSOR_HUB_16 | 11h     | SensorHub16_7       | SensorHub16_6 | SensorHub16_5 | SensorHub16_4         | SensorHub16_3           | SensorHub16_2 | SensorHub16_1 | SensorHub16_0 |

| SENSOR_HUB_17 | 12h     | SensorHub17_7       | SensorHub17_6 | SensorHub17_5 | SensorHub17_4         | SensorHub17_3           | SensorHub17_2 | SensorHub17_1 | SensorHub17_0 |

| SENSOR_HUB_18 | 13h     | SensorHub18_7       | SensorHub18_6 | SensorHub18_5 | SensorHub18_4         | SensorHub18_3           | SensorHub18_2 | SensorHub18_1 | SensorHub18_0 |

| MASTER_CONFIG | 14h     | RST_MASTER<br>_REGS | WRITE_ONCE    | START_CONFIG  | PASS_<br>THROUGH_MODE | 0                       | MASTER_ON     | AUX_SENS_ON1  | AUX_SENS_ON   |

| SLV0_ADD      | 15h     | slave0_add6         | slave0_add5   | slave0_add4   | slave0_add3           | slave0_add2             | slave0_add1   | slave0_add0   | rw_0          |

| SLV0_SUBADD   | 16h     | slave0_reg7         | slave0_reg6   | slave0_reg5   | slave0_reg4           | slave0_reg3             | slave0_reg2   | slave0_reg1   | slave0_reg0   |

| SLV0_CONFIG   | 17h     | SHUB_ODR_2          | SHUB_ODR_1    | SHUB_ODR_0    | 0                     | BATCH_EXT<br>_SENS_0_EN | Slave0_numop2 | Slave0_numop1 | Slave0_numop0 |

| SLV1_ADD      | 18h     | slave1_add6         | slave1_add5   | slave1_add4   | slave1_add3           | slave1_add2             | slave1_add1   | slave1_add0   | r_1           |

| SLV1_SUBADD   | 19h     | slave1_reg7         | slave1_reg6   | slave1_reg5   | slave1_reg4           | slave1_reg3             | slave1_reg2   | slave1_reg1   | slave1_reg0   |

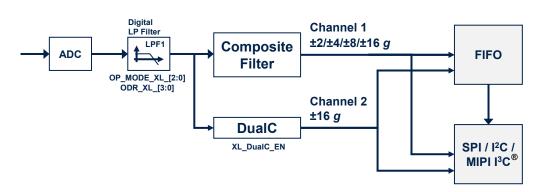

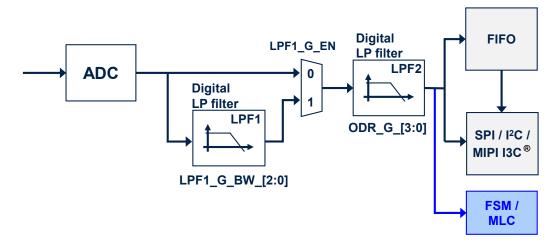

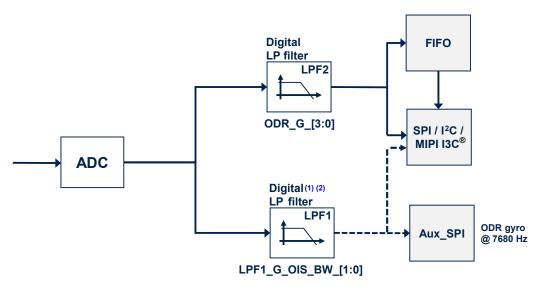

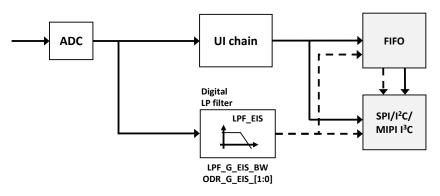

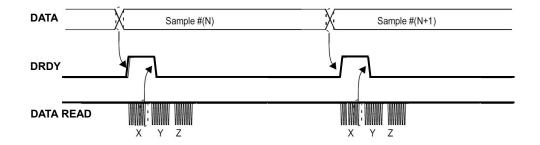

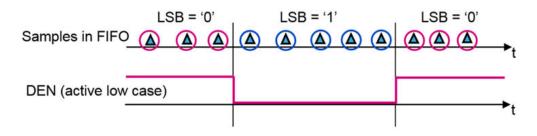

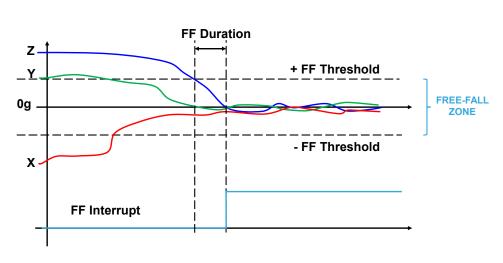

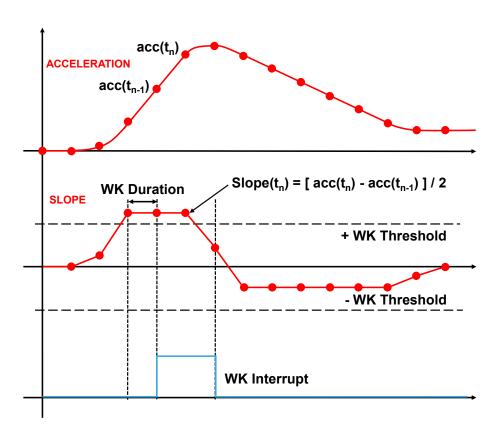

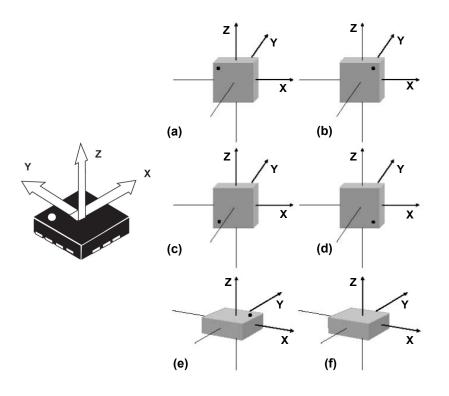

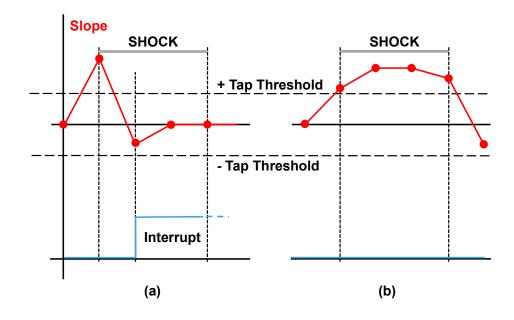

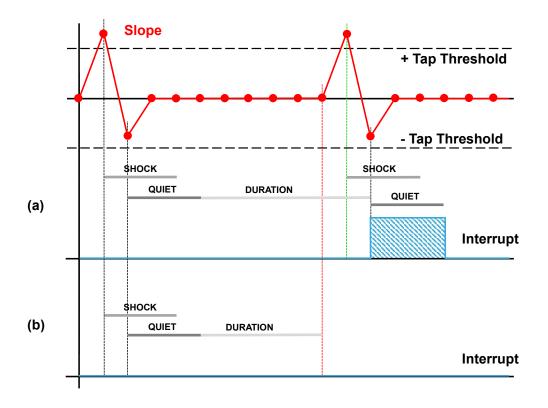

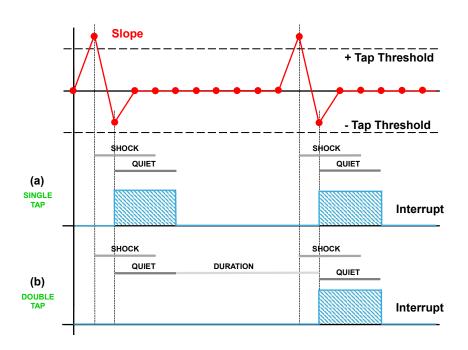

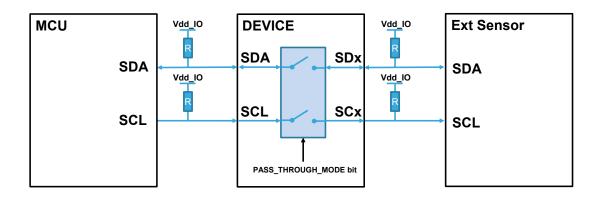

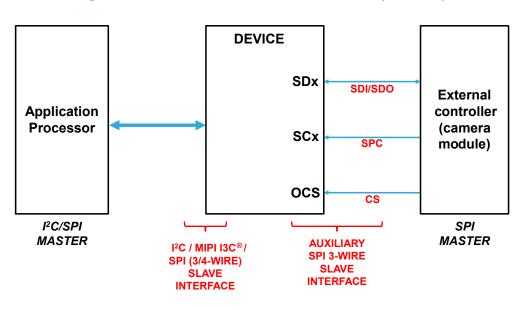

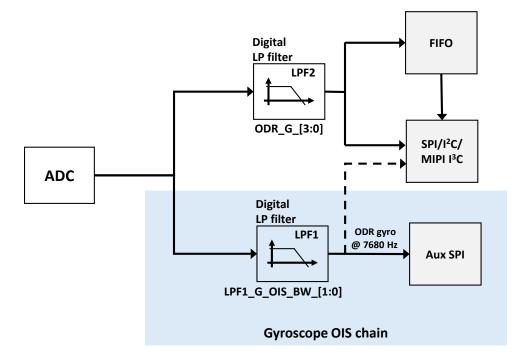

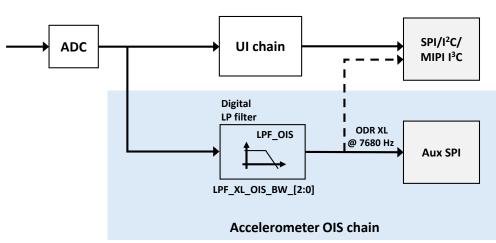

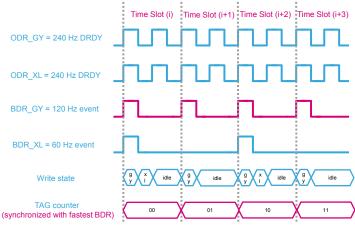

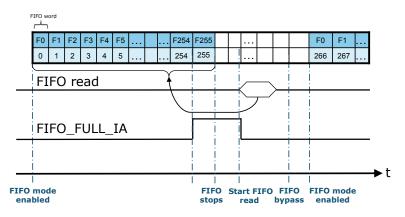

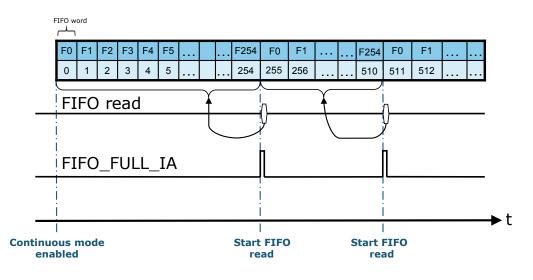

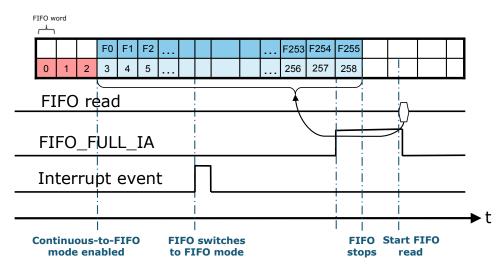

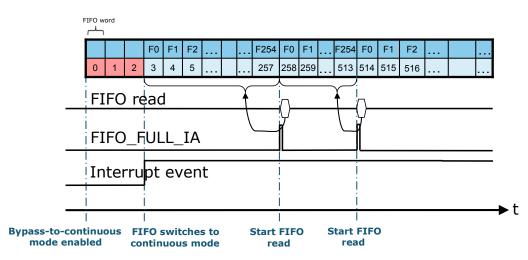

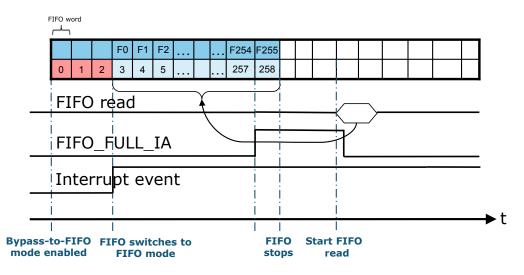

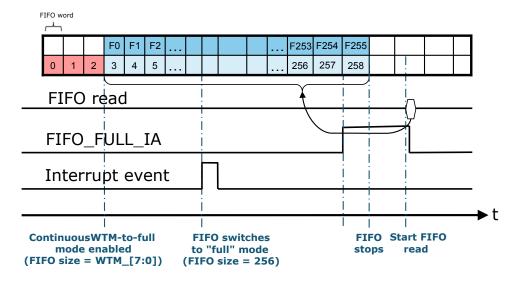

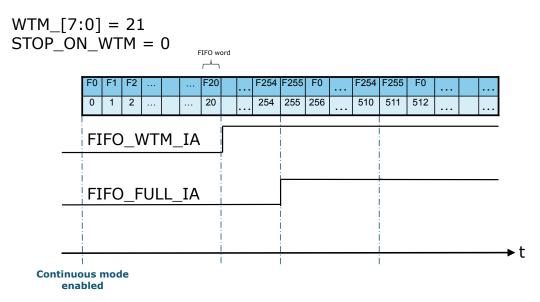

| SLV1_CONFIG   | 1Ah     | 0                   | 0             | 0             | 1                     | BATCH_EXT<br>_SENS_1_EN | Slave1_numop2 | Slave1_numop1 | Slave1_numop( |