#### MAX32664

# Ultra-Low Power Biometric Sensor Hub

## **General Description**

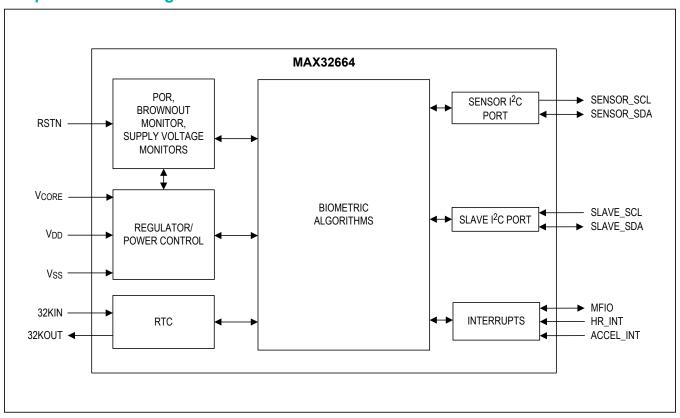

The MAX32664 is a sensor hub family with embedded firmware and algorithms for wearables. It seamlessly enables customer-desired sensor functionality, including communication with Maxim's optical sensor solutions and delivering raw or calculated data to the outside world. This is achieved while keeping overall system power consumption in check.

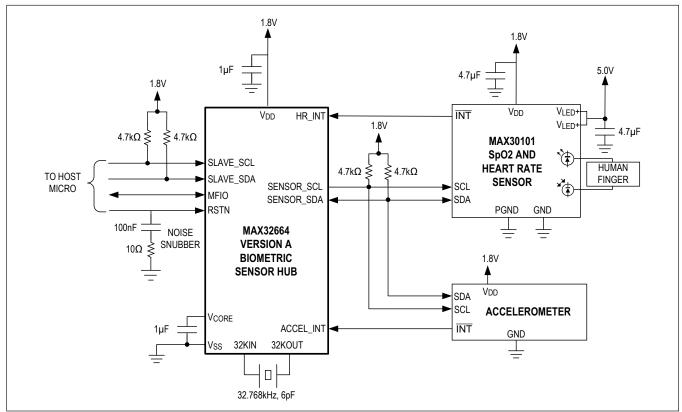

The MAX32664 Version A supports the MAX30101/MAX30102 high-sensitivity pulse oximeter and heart rate sensor for wearable health for finger-based applications.

The MAX32664 Version B supports the MAX86140/ MAX86141 for wrist-based monitoring.

The sensor hub interface provides a fast-mode, I<sup>2</sup>C slave interface to a microcontroller host. A second I<sup>2</sup>C interface is dedicated to communicating with sensors.

The tiny form factor (1.6mm x 1.6mm, 16-bump WLP) allows for integration into extremely small application devices.

## **Applications**

- Wearable Fitness

- Hearables

- Wearable Medical

- Portable Medical

- Mobile Devices

### **Benefits and Features**

- Biometric Sensor Hub Solution Enables Faster Time to Market

- Finger-Based (Version A) Algorithms Measure

- · Pulse Heart Rate

- Pulse Blood Oxygen Saturation (SpO2)

- Both Raw and Processed Data Are Available

- Basic Peripheral Mix Optimizes Size and Performance

- One Slave I<sup>2</sup>C for Communication to a Host Microcontroller

- One Master I<sup>2</sup>C for Communication with Sensors

- 32.768kHz RTC

- FIFO Provides Minimal Host Processor Interaction

- · Secure, Authenticated Firmware Upgrades

Ordering Information appears at end of data sheet.

# **Simplified Block Diagram**

## Ultra-Low Power Biometric Sensor Hub

## **Absolute Maximum Ratings**

| (All voltages with respect to V <sub>SS</sub> , unless otherwise noted.) | Output Current (sink) by Any Digital Pin25mA   |

|--------------------------------------------------------------------------|------------------------------------------------|

| V <sub>CORE</sub> 0.3V to +1.21V                                         | Output Current (source) by Any Digital Pin25mA |

| V <sub>DD</sub> 0.3V to +3.63V                                           | Operating Temperature Range40°C to +105°C      |

| 32KIN, 32KOUT0.3V to V <sub>DD</sub> + 0.3V                              | Storage Temperature Range65°C to +150°C        |

| RSTN0.3V to V <sub>DD</sub> + 0.3V                                       | Soldering Temperature (reflow)+260°C           |

| Total Current into All Digital Pins Combined (sink) 100mA                |                                                |

| Vee 100mA                                                                |                                                |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **Package Information**

### **16 WLP**

| Package Code                           | W161K1+1                       |  |  |  |

|----------------------------------------|--------------------------------|--|--|--|

| Outline Number                         | 21-100241                      |  |  |  |

| Land Pattern Number                    | Refer to Application Note 1891 |  |  |  |

| Thermal Resistance, Four-Layer Board:  |                                |  |  |  |

| Junction to Ambient (θ <sub>JA</sub> ) | 66.34 °C/W                     |  |  |  |

| Junction to Case $(\theta_{JC})$       | N/A                            |  |  |  |

For the latest package outline information and land patterns (footprints), go to <a href="www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to www.maximintegrated.com/thermal-tutorial.

## **Electrical Characteristics**

(Limits are 100% tested at  $T_A = +25$ °C and  $T_A = +105$ °C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization. Specifications marked GBD are guaranteed by design and not production tested. Specifications to the minimum operating temperature are guaranteed by design and are not production tested.)

| PARAMETER                                                          | SYMBOL              | CONDITIONS                                                       | MIN                      | TYP    | MAX                      | UNITS |

|--------------------------------------------------------------------|---------------------|------------------------------------------------------------------|--------------------------|--------|--------------------------|-------|

| POWER SUPPLIES                                                     |                     |                                                                  |                          |        |                          |       |

| Supply Voltage                                                     | $V_{DD}$            |                                                                  | 1.71                     | 1.8    | 3.63                     | V     |

| Power-Fail Reset Voltage                                           | V <sub>RST</sub>    | Monitors V <sub>DD</sub>                                         | 1.63                     |        | 1.71                     | V     |

| Power-On Reset Voltage                                             | V <sub>POR</sub>    | Monitors V <sub>DD</sub>                                         |                          | 1.4    |                          | V     |

| DIGITAL I/O                                                        |                     |                                                                  |                          |        |                          |       |

| Input Low Voltage for RSTN, SLAVE_SCL                              | VIL_RSTN            |                                                                  |                          |        | 0.3 ×<br>V <sub>DD</sub> | V     |

| Input High Voltage for All GPIO, RSTN                              | VIH_RSTN            |                                                                  | 0.7 ×<br>V <sub>DD</sub> |        |                          | V     |

| Output Low Voltage for SENSOR_SDA, SENSOR_SCL, SLAVE_SDA           | V <sub>OL_I2C</sub> | V <sub>DD</sub> = 1.71V, I <sub>OL</sub> = 2mA                   |                          | 0.2    | 0.4                      | V     |

| Output High Voltage for<br>SENSOR_SDA,<br>SENSOR_SCL,<br>SLAVE_SDA | V <sub>OH_I2C</sub> | V <sub>DD</sub> = 1.71V, I <sub>OH</sub> = 2mA,                  | V <sub>DD</sub> - 0.4    |        |                          | V     |

| Input Hysteresis (Schmitt)                                         | $V_{IHYS}$          |                                                                  |                          | 300    |                          | mV    |

| Input/Output Pin<br>Capacitance for All Pins                       | C <sub>IO</sub>     |                                                                  |                          | 4      |                          | pF    |

| Input Leakage Current Low                                          | I <sub>IL</sub>     | V <sub>IN</sub> = 0V, internal pullup disabled                   | -500                     |        | +500                     | nA    |

| Input Leakage Current High                                         | I <sub>IH</sub>     | V <sub>IN</sub> = 3.6V, internal pulldown disabled               | -500                     |        | +500                     | nA    |

| Input Pullup Resistor to RSTN                                      | R <sub>PU_VDD</sub> | Pullup to V <sub>DD</sub> = 3.63V                                |                          | 10.5   |                          | kΩ    |

| CLOCKS                                                             |                     |                                                                  |                          |        |                          |       |

| System Clock Frequency                                             | fsys_clk            |                                                                  |                          | 96     |                          | MHz   |

| RTC Input Frequency                                                | f <sub>32KIN</sub>  | 32.768kHz watch crystal, $C_L$ = 6pF,<br>ESR < 90kΩ, $C_0$ < 2pF |                          | 32.768 |                          | kHz   |

| RTC Operating Current                                              | I <sub>RTC</sub>    | All power modes, RTC enabled                                     |                          | 0.57   |                          | μA    |

| RTC Power-Up Time                                                  | t <sub>RTC</sub> ON |                                                                  |                          | 250    |                          | ms    |

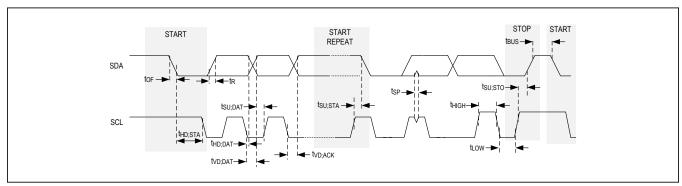

## Electrical Characteristics—I<sup>2</sup>C

(Limits are 100% tested at  $T_A$  = +25°C and  $T_A$  = +105°C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization. Specifications marked GBD are guaranteed by design and not production tested. Specifications to the minimum operating temperature are guaranteed by design and are not production tested.)

| PARAMETER                                           | SYMBOL              | CONDITIONS                                                | MIN | TYP | MAX | UNITS |

|-----------------------------------------------------|---------------------|-----------------------------------------------------------|-----|-----|-----|-------|

| FAST MODE                                           |                     |                                                           | •   |     |     |       |

| Output Fall Time                                    | t <sub>OF</sub>     | From V <sub>OL_I2C(MIN)</sub> to V <sub>OL_I2C(MAX)</sub> |     | 150 |     | ns    |

| Pulse Width Suppressed by Input Filter              | t <sub>SP</sub>     |                                                           |     | 75  |     | ns    |

| SCL Clock Frequency                                 | f <sub>SCL</sub>    |                                                           | 0   |     | 400 | kHz   |

| Low Period SCL Clock                                | $t_{LOW}$           |                                                           | 1.3 |     |     | μs    |

| High Time SCL Clock                                 | tHIGH               |                                                           | 0.6 |     |     | μs    |

| Setup Time for Repeated Start Condition             | t <sub>SU;STA</sub> |                                                           | 0.6 |     |     | μs    |

| Hold Time for Repeated Start Condition              | t <sub>HD;STA</sub> |                                                           | 0.6 |     |     | μs    |

| Data Setup Time                                     | t <sub>SU;DAT</sub> |                                                           |     | 125 |     | ns    |

| Data Hold Time                                      | t <sub>HD;DAT</sub> |                                                           |     | 10  |     | ns    |

| Rise Time for SDA and SCL                           | t <sub>R</sub>      |                                                           |     | 30  |     | ns    |

| Fall Time for SDA and SCL                           | $t_F$               |                                                           |     | 30  |     | ns    |

| Setup Time for a Stop<br>Condition                  | t <sub>SU;STO</sub> |                                                           | 0.6 |     |     | μs    |

| Bus Free Time Between a<br>Stop and Start Condition | t <sub>BUS</sub>    |                                                           | 1.3 |     |     | μs    |

| Data Valid Time                                     | t <sub>VD;DAT</sub> |                                                           | 0.9 |     |     | μs    |

| Data Valid Acknowledge<br>Time                      | t <sub>VD;ACK</sub> |                                                           | 0.9 |     |     | μs    |

Figure 1. I<sup>2</sup>C Timing Diagram

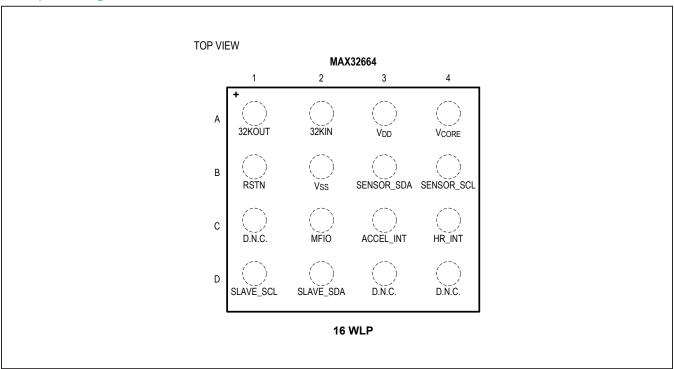

# **Bump Configuration**

# **Bump Description**

| BUMP  | NAME              | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| POWER |                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| A3    | V <sub>DD</sub>   | Digital Supply Voltage. This pin must be bypassed to $V_{SS}$ with a 1.0 $\mu$ F capacitor as close as possible to the package. The device can operate solely from this one power supply pin.                                                                                                                                                                                                                                                                                                                                                                                                      |

| A4    | V <sub>CORE</sub> | Core Supply Voltage. This pin must be left open-circuit. This pin must always be bypassed to $V_{SS}$ with a $1.0\mu F$ capacitor as close as possible to the package.                                                                                                                                                                                                                                                                                                                                                                                                                             |

| B2    | V <sub>SS</sub>   | Digital Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| CLOCK |                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| A2    | 32KIN             | 32.768kHz Crystal Oscillator Input. Connect a 32.768kHz crystal between 32KIN and 32KOUT for RTC operation. Optionally, an external clock source can be driven on 32KIN if the 32KOUT pin is left unconnected.                                                                                                                                                                                                                                                                                                                                                                                     |

| A1    | 32KOUT            | 32.768kHz Crystal Oscillator Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| RESET |                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| B1    | RSTN              | Hardware Power Reset (Active-Low) Input. The device remains in reset while this pin is in its active state. When the pin transitions to its inactive state, the device performs a POR reset (resetting all logic on all supplies except for real-time clock circuitry) and begins execution. This pin is internally connected with an internal pullup to the V <sub>DD</sub> supply as indicated in the <i>Electrical Characteristics</i> table. Add and place a noise snubber circuit as close as possible to the device, with component values shown in the <i>Typical Application Circuit</i> . |

## **Pin Description (continued)**

| BUMP             | NAME           | E FUNCTION                                                                                                                                                                                                                                                                   |  |  |  |

|------------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| I <sup>2</sup> C |                |                                                                                                                                                                                                                                                                              |  |  |  |

| D1               | SLAVE_SCL      | Slave SCL. This is the I <sup>2</sup> C slave SCL that should be connected to the host microprocessor I <sup>2</sup> C master SCL.                                                                                                                                           |  |  |  |

| D2               | SLAVE_SDA      | Slave SDA. This is the I <sup>2</sup> C slave SDA that should be connected to the host microprocessor I <sup>2</sup> C master SDA.                                                                                                                                           |  |  |  |

| B4               | SENSOR_SCL     | Sensor SCL. This is the I <sup>2</sup> C master SCL that should be connected to the I <sup>2</sup> C slave SCL on the slave sensors.                                                                                                                                         |  |  |  |

| В3               | SENSOR_SDA     | Sensor SDA. This is the I <sup>2</sup> C master SDA that should be connected to the I <sup>2</sup> C slave SDA on the slave sensors.                                                                                                                                         |  |  |  |

| INTERR           | UPTS           |                                                                                                                                                                                                                                                                              |  |  |  |

| C4               | HR_INT         | Heart Rate Monitor Interrupt Input. This pin connects to the heart rate monitor sensor interrupt output.                                                                                                                                                                     |  |  |  |

| C3               | ACCEL_INT      | Accelerometer Interrupt Input. This pin connects to the accelerometer sensor interrupt output.                                                                                                                                                                               |  |  |  |

| C2               | MFIO           | Multifunction IO. This pin provides different functions: MFIO asserts low as an output when the sensor hub needs to communicate with the host controller; the pin acts as an input and causes the sensor hub to enter bootloader mode if the MFIO pin is low during a reset. |  |  |  |

| DO NOT           | DO NOT CONNECT |                                                                                                                                                                                                                                                                              |  |  |  |

| C1, D3,<br>D4    | D.N.C.         | Do Not Connect. Internally connected. Do not make any electrical connection, including V <sub>SS</sub> , to these pins.                                                                                                                                                      |  |  |  |

## **Detailed Description**

The MAX32664 is a sensor hub family with embedded firmware and algorithms for wearables. It seamlessly enables customer-desired sensor functionality, including communication with Maxim's optical sensor solutions and delivering raw or calculated data to the outside world. This is achieved while keeping overall system power consumption in check.

The MAX32664 Version A supports the MAX30101/MAX30102 high-sensitivity pulse oximeter and heart-rate sensor for wearable health for finger-based applications.

The sensor hub interface provides an fast-mode I<sup>2</sup>C slave interface to transmit commands and data to a microcontroller host. A second I<sup>2</sup>C interface is dedicated to communication with sensors.

The sampling of the sensors is derived from the 32.768kHz real-time clock. The sampling rate is user-configurable to minimize power consumption.

#### **Algorithmic Processing**

#### **Finger Heart Rate Algorithms**

The MAX32664 Version A performs finger-based heart rate and blood oxygen saturation (SpO2) monitoring. The embedded algorithm uses digital filtering, pressure/position compensation, advanced R-wave detection, and automatic gain control to determine the heart rate in beats per minute while minimizing power. Also, the Maxim Integrated sensor hardware has built-in ambient light rejection to minimize background noise. SpO2 results are reported as percentage of hemoglobin that is saturated with oxygen. The calibration values for SpO2 configuration should be performed while using the end product.

# Ultra-Low Power Biometric Sensor Hub

#### I<sup>2</sup>C Interface

The I<sup>2</sup>C interface is a bidirectional, two-wire serial bus that provides a medium-speed communications network. The device provides two I<sup>2</sup>C busses.

The I<sup>2</sup>C sensor bus is dedicated to communication with the sensors. The characteristics of this bus are not user-configurable.

The I<sup>2</sup>C slave bus connects the sensor hub to a host system or microcontroller that acts as an I<sup>2</sup>C master. It provides the following features:

- Slave address 0x55

- Fast-mode (400kbps) transfer rate

- Supports standard 7-bit addressing or 10-bit addressing

- RESTART condition

- Interactive receive mode

- Tx FIFO preloading

- Support for clock stretching to allow slower slave devices to operate on higher speed busses

- Internal filter to reject noise spikes

- · Receiver FIFO depth of 8 bytes

- Transmitter FIFO depth of 8 bytes

## **Typical Application Circuit**

# **Ordering Information**

| PART            | VERSION | BOOT LOADER | PIN-PACKAGE                                   |

|-----------------|---------|-------------|-----------------------------------------------|

| MAX32664GWEA+   | А       | Yes         | 16 WLP (1.6mm x 1.6mm x 0.65mm, 0.35mm pitch) |

| MAX32664GWEA+T  | А       | Yes         | 16 WLP (1.6mm x 1.6mm x 0.65mm, 0.35mm pitch) |

| MAX32664GWEB+*  | В       | Yes         | 16 WLP (1.6mm x 1.6mm x 0.65mm, 0.35mm pitch) |

| MAX32664GWEB+T* | В       | Yes         | 16 WLP (1.6mm x 1.6mm x 0.65mm, 0.35mm pitch) |

<sup>+</sup>Denotes a lead(Pb)-free/RoHS-compliant package.

T = Tape and reel. Full reel.

<sup>\*</sup>Future product—contact factory for availability.

## **Revision History**

| REVISION<br>NUMBER | REVISION DATE | DESCRIPTION                                                         | PAGES<br>CHANGED |

|--------------------|---------------|---------------------------------------------------------------------|------------------|

| 0                  | 4/18          | Initial release                                                     | _                |

| 0.1                |               | Added future product references to MAX32664GWEB+ and MAX32664GWEB+T | 9                |

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim Integrated's website at www.maximintegrated.com.

Maxim Integrated cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim Integrated product. No circuit patent licenses are implied. Maxim Integrated reserves the right to change the circuitry and specifications without notice at any time. The parametric values (min and max limits) shown in the Electrical Characteristics table are guaranteed. Other parametric values quoted in this data sheet are provided for guidance.