# SiFive FE310-G002 Manual v19p05

© SiFive, Inc.

# SiFive FE310-G002 Manual

#### **Proprietary Notice**

Copyright © 2019, SiFive Inc. All rights reserved.

Information in this document is provided "as is," with all faults.

SiFive expressly disclaims all warranties, representations, and conditions of any kind, whether express or implied, including, but not limited to, the implied warranties or conditions of merchantability, fitness for a particular purpose and non-infringement.

SiFive does not assume any liability rising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation indirect, incidental, special, exemplary, or consequential damages.

SiFive reserves the right to make changes without further notice to any products herein.

#### **Release Information**

| Version | Date           | Changes                      |

|---------|----------------|------------------------------|

| v19p04  | April 11, 2019 | Initial release              |

| v19p05  | May 08, 2019   | Correct UART1 pin assignment |

# **Contents**

| 1 | Int  | roduction                                   | 8  |

|---|------|---------------------------------------------|----|

|   | 1.1  | FE310-G002 Overview                         | 8  |

|   | 1.2  | E31 RISC-V Core                             | 10 |

|   | 1.3  | Interrupts                                  | 10 |

|   | 1.4  | On-Chip Memory System                       | 11 |

|   | 1.5  | Always-On (AON) Block                       | 11 |

|   | 1.6  | GPIO Complex                                | 11 |

|   | 1.7  | Universal Asynchronous Receiver/Transmitter | 11 |

|   | 1.8  | Hardware Serial Peripheral Interface (SPI)  | 11 |

|   | 1.9  | Pulse Width Modulation                      | 12 |

|   | 1.10 | I <sup>2</sup> C                            | 12 |

|   | 1.11 | Debug Support                               | 12 |

| 3 | E3   | 1 RISC-V Core                               | 15 |

|   | 3.1  | Instruction Memory System                   |    |

|   |      | .1.1 I-Cache Reconfigurability              |    |

|   | 3.2  | Instruction Fetch Unit                      |    |

|   | 3.3  | Execution Pipeline                          |    |

|   | 3.4  | Data Memory System                          |    |

|   | 3.5  | Atomic Memory Operations                    |    |

|   | 3.6  | Supported Modes                             |    |

|   | 3.7  | Physical Memory Protection (PMP)            | 18 |

|   | 3    | .7.1 Functional Description                 |    |

|   | 3    | .7.2 Region Locking                         | 18 |

|   | 3.8  | Hardware Performance Monitor                | 19 |

|   |      |                                             |    |

| 4 | Me   | mory Map                                    | 21 |

| 5 | Во         | ot F | Process                                                  | 23 |

|---|------------|------|----------------------------------------------------------|----|

|   | 5.1        | Res  | et Vector                                                | 23 |

|   | 5          | .1.1 | Mask ROM (MROM)                                          | 24 |

|   | 5          | .1.2 | One-Time Programmable (OTP) Memory                       | 24 |

|   | 5          | .1.3 | Quad SPI Flash Controller (QSPI)                         | 24 |

| _ | <b>~</b> ! |      |                                                          |    |

| 6 |            |      | Generation                                               |    |

|   | 6.1        |      | ck Generation Overview                                   |    |

|   | 6.2        | PRO  | CI Address Space Usage                                   | 26 |

|   | 6.3        | Inte | rnal Trimmable Programmable 72 MHz Oscillator (HFROSC)   | 26 |

|   | 6.4        | Exte | ernal 16 MHz Crystal Oscillator (HFXOSC)                 | 27 |

|   | 6.5        | Inte | rnal High-Frequency PLL (HFPLL)                          | 28 |

|   | 6.6        | PLL  | Output Divider                                           | 30 |

|   | 6.7        | Inte | rnal Programmable Low-Frequency Ring Oscillator (LFROSC) | 31 |

|   | 6.8        | Alte | rnate Low-Frequency Clock (LFALTCLK)                     | 32 |

|   | 6.9        | Cloc | ck Summary                                               | 32 |

| 7 | Po         | wer  | Modes                                                    | 33 |

|   | 7.1        | Run  | Mode                                                     | 33 |

|   | 7.2        | Wait | t Mode                                                   | 33 |

|   | 7.3        | Slee | ep Mode                                                  | 33 |

| _ | 14         |      |                                                          |    |

| 8 | int        |      | ıpts                                                     |    |

|   | 8.1        |      | rrupt Concepts                                           |    |

|   | 8.2        | Inte | rrupt Operation                                          | 36 |

|   | 8          | .2.1 | Interrupt Entry and Exit                                 | 36 |

|   | 8.3        | Inte | rrupt Control Status Registers                           | 37 |

|   | 8          | .3.1 | Machine Status Register (mstatus)                        | 37 |

|   | 8          | .3.2 | Machine Trap Vector (mtvec)                              | 37 |

|   | 0          |      | Machine Interrupt Enable (mie)                           | 20 |

|   | ŏ          | .3.3 | wasimie merupt Enable (mre)                              | 39 |

|   |            | .3.3 | Machine Interrupt Pending (mip)                          |    |

|   | 8          |      |                                                          | 39 |

|    | 8.5  | Interrupt Latency                            | 41 |

|----|------|----------------------------------------------|----|

| 9  | Co   | re-Local Interruptor (CLINT)                 | 42 |

|    | 9.1  | CLINT Memory Map                             |    |

|    | 9.2  | MSIP Registers                               |    |

|    | 9.3  | Timer Registers                              |    |

| 10 | Р    | latform-Level Interrupt Controller (PLIC)    | 44 |

|    | 10.1 | Memory Map                                   | 44 |

|    | 10.2 | Interrupt Sources                            | 45 |

|    | 10.3 | Interrupt Priorities                         | 46 |

|    | 10.4 | Interrupt Pending Bits                       | 46 |

|    | 10.5 | Interrupt Enables                            | 47 |

|    | 10.6 | Priority Thresholds                          | 48 |

|    | 10.7 | Interrupt Claim Process                      | 48 |

|    | 10.8 | Interrupt Completion                         | 49 |

| 11 | . Е  | rror Device                                  | 51 |

| 12 | . 0  | ne-Time Programmable Memory (OTP) Peripheral | 52 |

|    | 12.1 | Memory Map                                   | 52 |

|    | 12.2 | Programmed-I/O lock register (otp_lock)      | 53 |

|    | 12.3 | Programmed-I/O Sequencing                    | 54 |

|    | 12.4 | Read sequencer control register (otp_rsctr1) | 54 |

|    | 12.5 | OTP Programming Warnings                     | 54 |

|    | 12.6 | OTP Programming Procedure                    | 55 |

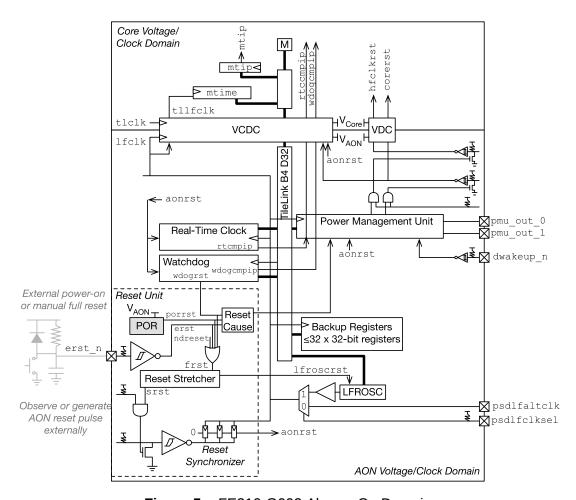

| 13 | A    | lways-On (AON) Domain                        | 56 |

|    | 13.1 | AON Power Source                             | 57 |

|    | 13.2 | AON Clocking                                 | 57 |

|    | 13.3 | AON Reset Unit                               | 57 |

|    | 13.4 | Power-On Reset Circuit                       | 57 |

|    | 13.5 | External Reset Circuit                       | 58 |

|    | 13.6 | Reset Cause                                  | 58 |

|    | 13.7  | Watchdog Timer (WDT)                                      | 58 |

|----|-------|-----------------------------------------------------------|----|

|    | 13.8  | Real-Time Clock (RTC)                                     | 58 |

|    | 13.9  | Backup Registers                                          | 58 |

|    | 13.10 | Power-Management Unit (PMU)                               | 58 |

|    | 13.11 | AON Memory Map                                            | 58 |

|    |       |                                                           |    |

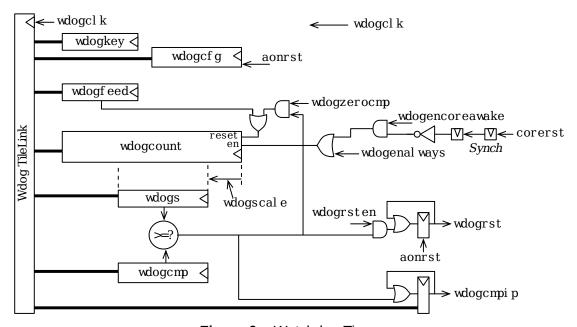

| 14 | Wa    | tchdog Timer (WDT)                                        |    |

|    | 14.1  | Watchdog Count Register (wdogcount)                       | 61 |

|    | 14.2  | Watchdog Clock Selection                                  | 62 |

|    | 14.3  | Watchdog Configuration Register (wdogcfg)                 | 62 |

|    | 14.4  | Watchdog Compare Register (wdogcmp)                       | 63 |

|    | 14.5  | Watchdog Key Register (wdogkey)                           | 63 |

|    | 14.6  | Watchdog Feed Address (wdogfeed)                          | 64 |

|    | 14.7  | Watchdog Configuration                                    | 64 |

|    | 14.8  | Watchdog Resets                                           | 64 |

|    | 14.9  | Watchdog Interrupts (wdogip0)                             | 64 |

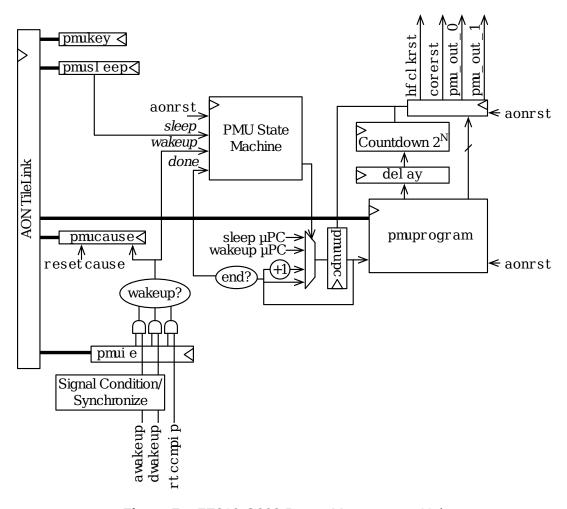

| 16 | Do    | war Managamant Linit (DMLI)                               | 25 |

| 15 |       | wer-Management Unit (PMU)                                 |    |

|    | 15.1  | PMU Overview                                              |    |

|    | 15.2  | Memory Map                                                |    |

|    | 15.3  | PMU Key Register (pmukey)                                 |    |

|    | 15.4  | PMU Program                                               |    |

|    | 15.5  | Initiate Sleep Sequence Register (pmusleep)               |    |

|    | 15.6  | Wakeup Signal Conditioning                                |    |

|    | 15.7  | PMU Interrupt Enables (pmuie) and Wakeup Cause (pmucause) | 69 |

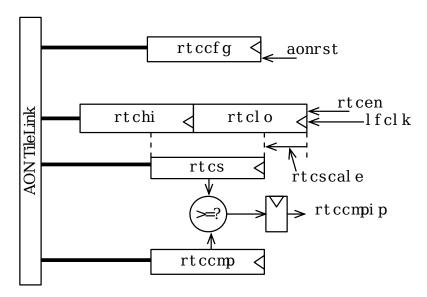

| 16 | Re    | al-Time Clock (RTC)                                       | 71 |

|    | 16.1  | RTC Count Registers (rtccounthi/rtccountlo)               | 71 |

|    | 16.2  | RTC Configuration Register (rtccfg)                       | 72 |

|    | 16.3  | RTC Compare Register (rtccmp)                             | 72 |

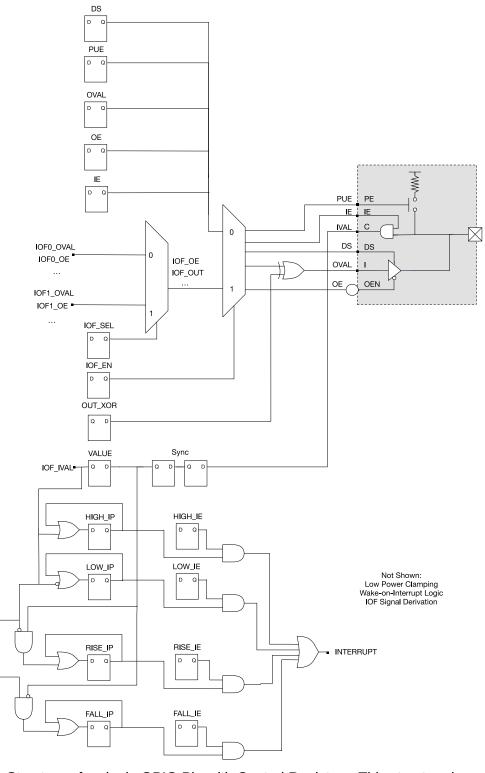

| 17 | Ge    | neral Purpose Input/Output Controller (GPIO)              | 74 |

|    | 17.1  | GPIO Instance in FE310-G002                               | 76 |

| 17.2  | Memory Map                                        | 76 |

|-------|---------------------------------------------------|----|

| 17.3  | Input / Output Values                             | 76 |

| 17.4  | Interrupts                                        | 77 |

| 17.5  | Internal Pull-Ups                                 | 77 |

| 17.6  | Drive Strength                                    | 77 |

| 17.7  | Output Inversion                                  | 77 |

| 17.8  | HW I/O Functions (IOF)                            | 77 |

| 18 Uı | niversal Asynchronous Receiver/Transmitter (UART) | 79 |

| 18.1  | UART Overview                                     | 79 |

| 18.2  | UART Instances in FE310-G002                      | 79 |

| 18.3  | Memory Map                                        | 80 |

| 18.4  | Transmit Data Register (txdata)                   | 80 |

| 18.5  | Receive Data Register (rxdata)                    | 80 |

| 18.6  | Transmit Control Register (txctrl)                | 81 |

| 18.7  | Receive Control Register (rxctrl)                 | 81 |

| 18.8  | Interrupt Registers (ip and ie)                   | 82 |

| 18.9  | Baud Rate Divisor Register (div)                  | 82 |

| 19 Se | erial Peripheral Interface (SPI)                  | 84 |

| 19.1  | SPI Overview                                      |    |

| 19.2  | SPI Instances in FE310-G002                       | 84 |

| 19.3  | Memory Map                                        | 85 |

| 19.4  | Serial Clock Divisor Register (sckdiv)            | 86 |

| 19.5  | Serial Clock Mode Register (sckmode)              | 87 |

| 19.6  | Chip Select ID Register (csid)                    | 87 |

| 19.7  | Chip Select Default Register (csdef)              | 88 |

| 19.8  | Chip Select Mode Register (csmode)                | 88 |

| 19.9  | Delay Control Registers (delay0 and delay1)       | 89 |

| 19.10 | Frame Format Register (fmt)                       | 89 |

| 19.11 | Transmit Data Register (t×data)                   | 90 |

| 19.12 | Receive Data Register (rxdata)                    | 91 |

| 19.13 | Transmit Watermark Register (txmark)              | 91 |

|    | 19.14 | Red                 | ceive Watermark Register (rxmark)                     | 92  |

|----|-------|---------------------|-------------------------------------------------------|-----|

|    | 19.15 | SPI                 | Interrupt Registers (ie and ip)                       | 92  |

|    | 19.16 | SPI                 | Flash Interface Control Register (fctrl)              | 93  |

|    | 19.17 | SPI                 | Flash Instruction Format Register (ffmt)              | 93  |

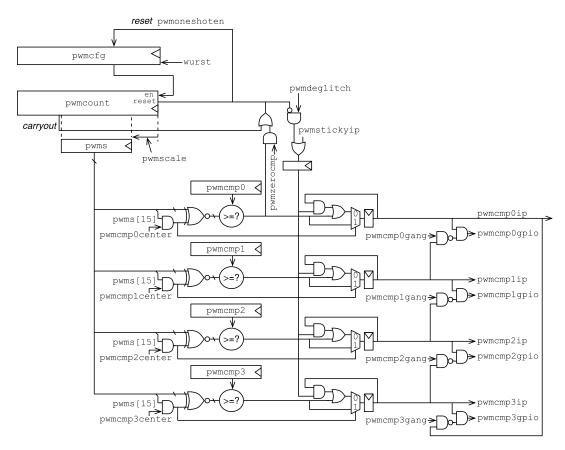

| 20 | ) Pu  | lse '               | Width Modulator (PWM)                                 | 94  |

|    | 20.1  | PWN                 | 1 Overview                                            | 94  |

|    | 20.2  | PWN                 | Instances in FE310-G002                               | 95  |

|    | 20.3  | PWN                 | 1 Memory Map                                          | 95  |

|    | 20.4  | PWN                 | 1 Count Register (pwmcount)                           | 96  |

|    | 20.5  | PWN                 | # Configuration Register (pwmcfg)                     | 97  |

|    | 20.6  | Scal                | ed PWM Count Register (pwms)                          | 98  |

|    | 20.7  | PWN                 | // Compare Registers (pwmcmp0-pwmcmp3)                | 98  |

|    | 20.8  | Degl                | itch and Sticky Circuitry                             | 99  |

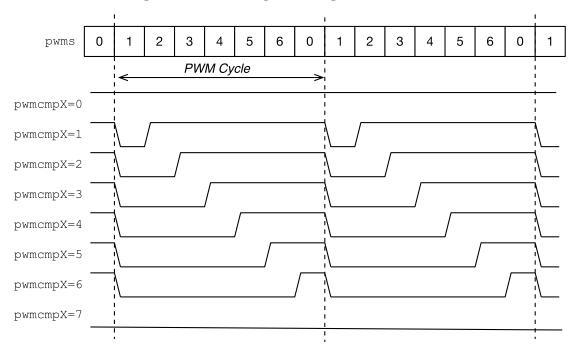

|    | 20.9  | Gene                | erating Left- or Right-Aligned PWM Waveforms          | 100 |

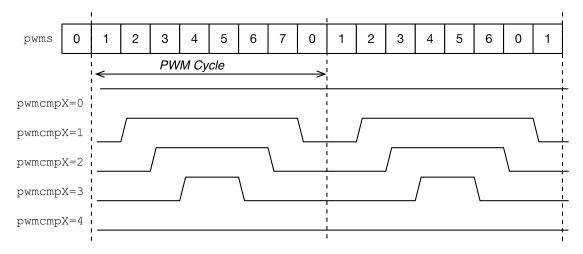

|    | 20.10 | Gei                 | nerating Center-Aligned (Phase-Correct) PWM Waveforms | 100 |

|    | 20.11 | Gei                 | nerating Arbitrary PWM Waveforms using Ganging        | 101 |

|    | 20.12 | Gei                 | nerating One-Shot Waveforms                           | 102 |

|    | 20.13 | PW                  | M Interrupts                                          | 102 |

| 21 | . Int | er-Ir               | ntegrated Circuit (I²C) Master Interface              | 103 |

|    | 21.1  | I <sup>2</sup> C II | nstance in FE310-G002                                 | 103 |

|    |       |                     |                                                       |     |

| 22 | 2 De  | bug                 |                                                       | 104 |

|    | 22.1  | Debu                | ug CSRs                                               | 104 |

|    | 22    | .1.1                | Trace and Debug Register Select (tselect)             | 104 |

|    | 22    | .1.2                | Trace and Debug Data Registers (tdata1-3)             | 105 |

|    | 22    | .1.3                | Debug Control and Status Register (dcsr)              | 106 |

|    | 22    | .1.4                | Debug PC dpc                                          | 106 |

|    | 22    | .1.5                | Debug Scratch dscratch                                | 106 |

|    | 22.2  | Brea                | kpoints                                               | 106 |

|    | 22    | .2.1                | Breakpoint Match Control Register mcontrol            | 106 |

|    | 22    | .2.2                | Breakpoint Match Address Register (maddress)          | 108 |

|    | 22.  | .2.3 | Breakpoint Execution                               | 108 |

|----|------|------|----------------------------------------------------|-----|

|    | 22.  | .2.4 | Sharing Breakpoints Between Debug and Machine Mode | 109 |

|    | 22.3 | Debu | g Memory Map                                       | 109 |

|    | 22.  | .3.1 | Debug RAM and Program Buffer (0x300–0x3FF)         | 109 |

|    | 22.  | .3.2 | Debug ROM (0x800-0xFFF)                            | 109 |

|    | 22.  | .3.3 | Debug Flags (0x100-0x110, 0x400-0x7FF)             | 110 |

|    | 22.  | .3.4 | Safe Zero Address                                  | 110 |

|    |      |      |                                                    |     |

| 23 | B De | bug  | Interface                                          | 111 |

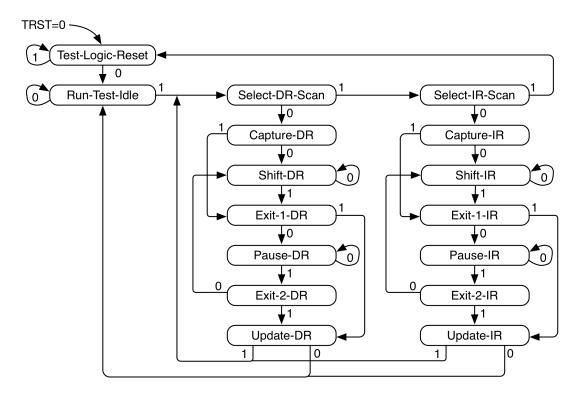

|    | 23.1 | JTAG | TAPC State Machine                                 | 111 |

|    | 23.2 | Rese | tting JTAG Logic                                   | 112 |

|    | 23.3 | JTAG | Clocking                                           | 112 |

|    | 23.4 | JTAG | Standard Instructions                              | 113 |

|    | 23.5 | JTAG | Debug Commands                                     | 113 |

|    | _    | _    |                                                    |     |

| 24 | ⊦ Re | tere | nces                                               | 114 |

# Introduction

The FE310-G002 is the second revision of the General Purpose Freedom E300 family.

The FE310-G002 is built around the E31 Core Complex instantiated in the Freedom E300 platform and fabricated in the TSMC CL018G 180nm process. This manual serves as an architectural reference and integration guide for the FE310-G002.

The FE310-G002 is compatible with all applicable RISC-V standards, and this document should be read together with the official RISC-V user-level, privileged, and external debug architecture specifications.

#### 1.1 FE310-G002 Overview

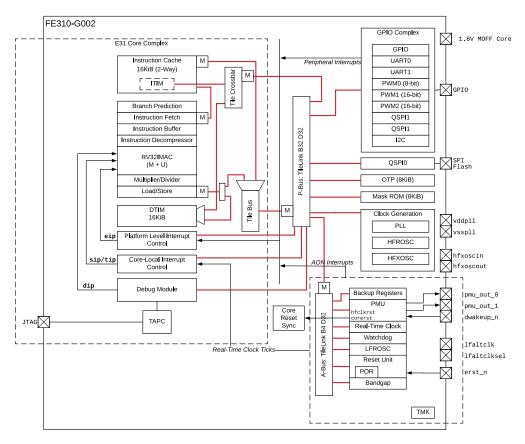

Figure 1 shows the overall block diagram of the FE310-G002.

A feature summary table can be found in Table 1.

Figure 1: FE310-G002 top-level block diagram.

| Feature             | Description                                                                                                                   | Available in QFN48           |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------|------------------------------|

| RISC-V Core         | 1× E31 RISC-V cores with machine and user mode,<br>16 KiB 2-way L1 I-cache, and 16 KiB data tightly integrated memory (DTIM). | •                            |

| Interrupts          | Software and timer interrupts, 52 peripheral interrupts connected to the PLIC with 7 levels of priority.                      | <b>✓</b>                     |

| UART 0              | Universal Asynchronous/Synchronous Transmitters for serial communication.                                                     | <b>/</b>                     |

| UART 1              | Universal Asynchronous/Synchronous Transmitters for serial communication.                                                     | <b>*</b>                     |

| QSPI 0              | Serial Peripheral Interface. QSPI 0 has 1 chip select signal.                                                                 | ✓<br>(4 DQ lines)            |

| SPI 1               | Serial Peripheral Interface. SPI 1 has 4 chip select signals.                                                                 | (3 CS lines)<br>(2 DQ lines) |

| SPI 2               | Serial Peripheral Interface. SPI 2 has 1 chip select signal.                                                                  |                              |

| PWM 0               | 8-bit Pulse-width modulator with 4 comparators.                                                                               | •                            |

| PWM 1               | 16-bit Pulse-width modulator with 4 comparators.                                                                              | •                            |

| PWM 2               | 16-bit Pulse-width modulator with 4 comparators.                                                                              | •                            |

| I <sup>2</sup> C 0  | Inter-Integrated Circuit (I <sup>2</sup> C) controller.                                                                       | •                            |

| GPIO                | 32 General Purpose I/O pins.                                                                                                  | •                            |

| Always On<br>Domain | Supports low-power operation and wakeup.                                                                                      | /                            |

**Table 1:** FE310-G002 Feature Summary.

#### 1.2 E31 RISC-V Core

The FE310-G002 includes a 32-bit E31 RISC-V core, which has a high-performance single-issue in-order execution pipeline, with a peak sustainable execution rate of one instruction per clock cycle. The E31 core supports Machine and User privilege modes as well as standard Multiply, Atomic, and Compressed RISC-V extensions (RV32IMAC).

The core is described in more detail in Chapter 3.

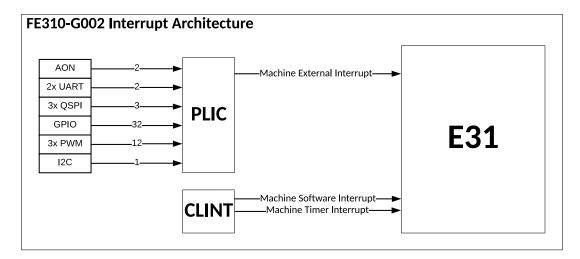

# 1.3 Interrupts

The FE310-G002 includes a RISC-V standard platform-level interrupt controller (PLIC), which supports 52 global interrupts with 7 priority levels. The FE310-G002 also provides the standard RISC-V machine-mode timer and software interrupts via the Core-Local Interruptor (CLINT).

Interrupts are described in Chapter 8. The CLINT is described in Chapter 9. The PLIC is described in Chapter 10.

# 1.4 On-Chip Memory System

The E31 core has a(n) 2-way set-associative 16 KiB L1 instruction cache and a(n) 16 KiB L1 DTIM.

All cores have Physical Memory Protection (PMP) units.

The Level 1 memories are described in Chapter 3. The PMP is described in Section 3.7.

# 1.5 Always-On (AON) Block

The AON block contains the reset logic for the chip, an on-chip low-frequency oscillator, a watchdog timer, connections for an off-chip low-frequency oscillator, the real-time clock, a programmable power-management unit, and 32×32-bit backup registers that retain state while the rest of the chip is in a low-power mode.

The AON can be instructed to put the system to sleep. The AON can be programmed to exit sleep mode on a real-time clock interrupt or when the external digital wakeup pin, dwakeup\_n, is pulled low. The dwakeup\_n input supports wired-OR connections of multiple wakeup sources.

The Always-On block is described in Chapter 13.

#### 1.6 GPIO Complex

The GPIO complex manages the connection of digital I/O pads to digital peripherals, including SPI, UART, I<sup>2</sup>C, and PWM controllers, as well as for regular programmed I/O operations.

The GPIO complex is described in more detail in Chapter 17.

### 1.7 Universal Asynchronous Receiver/Transmitter

Multiple universal asynchronous receiver/transmitter (UARTs) are available and provide a means for serial communication between the FE310-G002 and off-chip devices.

The UART peripherals are described in Chapter 18.

# 1.8 Hardware Serial Peripheral Interface (SPI)

There are 3 serial peripheral interface (SPI) controllers. Each controller provides a means for serial communication between the FE310-G002 and off-chip devices, like quad-SPI Flash memory. Each controller supports master-only operation over single-lane, dual-lane, and quad-lane protocols. Each controller supports burst reads of 32 bytes over TileLink to accelerate instruction cache refills. 1 SPI controller can be programmed to support eXecute-In-Place (XIP) modes to reduce SPI command overhead on instruction cache refills.

The SPI interface is described in more detail in Chapter 19.

#### 1.9 Pulse Width Modulation

The pulse width modulation (PWM) peripheral can generate multiple types of waveforms on GPIO output pins and can also be used to generate several forms of internal timer interrupt.

The PWM peripherals are described in Chapter 20.

#### 1.10 I<sup>2</sup>C

The FE310-G002 has an I<sup>2</sup>C controller to communicate with external I<sup>2</sup>C devices, such as sensors, ADCs, etc.

The I<sup>2</sup>C is described in detail in Chapter 21.

#### 1.11 Debug Support

The FE310-G002 provides external debugger support over an industry-standard JTAG port, including 8 hardware-programmable breakpoints per hart.

Debug support is described in detail in Chapter 22, and the debug interface is described in Chapter 23.

# **List of Abbreviations and Terms**

| Term     | Definition                                                                                                                                                                                                |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BHT      | Branch History Table                                                                                                                                                                                      |

| ВТВ      | Branch Target Buffer                                                                                                                                                                                      |

| RAS      | Return-Address Stack                                                                                                                                                                                      |

| CLINT    | Core-Local Interruptor. Generates per-hart software interrupts and timer interrupts.                                                                                                                      |

| CLIC     | Core-Local Interrupt Controller. Configures priorities and levels for core local interrupts.                                                                                                              |

| hart     | HARdware Thread                                                                                                                                                                                           |

| DTIM     | Data Tightly Integrated Memory                                                                                                                                                                            |

| ITIM     | Instruction Tightly Integrated Memory                                                                                                                                                                     |

| JTAG     | Joint Test Action Group                                                                                                                                                                                   |

| LIM      | Loosely Integrated Memory. Used to describe memory space delivered in a SiFive Core Complex but not tightly integrated to a CPU core.                                                                     |

| PMP      | Physical Memory Protection                                                                                                                                                                                |

| PLIC     | Platform-Level Interrupt Controller. The global interrupt controller in a RISC-V system.                                                                                                                  |

| TileLink | A free and open interconnect standard originally developed at UC Berkeley.                                                                                                                                |

| RO       | Used to describe a Read Only register field.                                                                                                                                                              |

| RW       | Used to describe a Read/Write register field.                                                                                                                                                             |

| WO       | Used to describe a Write Only registers field.                                                                                                                                                            |

| WARL     | Write-Any Read-Legal field. A register field that can be written with any value, but returns only supported values when read.                                                                             |

| WIRI     | Writes-Ignored, Reads-Ignore field. A read-only register field reserved for future use. Writes to the field are ignored, and reads should ignore the value returned.                                      |

| WLRL     | Write-Legal, Read-Legal field. A register field that should only be written with legal values and that only returns legal value if last written with a legal value.                                       |

| WPRI     | Writes-Preserve Reads-Ignore field. A register field that might contain unknown information. Reads should ignore the value returned, but writes to the whole register should preserve the original value. |

# E31 RISC-V Core

This chapter describes the 32-bit E31 RISC-V processor core used in the FE310-G002. The E31 processor core comprises an instruction memory system, an instruction fetch unit, an execution pipeline, a data memory system, and support for global, software, and timer interrupts.

The E31 feature set is summarized in Table 2.

| Feature                               | Description                                                    |

|---------------------------------------|----------------------------------------------------------------|

| ISA                                   | RV32IMAC.                                                      |

| Instruction Cache                     | 16 KiB 2-way instruction cache.                                |

| Instruction Tightly Integrated Memory | The E31 has support for an ITIM with a maximum size of 8 KiB.  |

| Data Tightly Integrated Memory        | 16 KiB DTIM.                                                   |

| Modes                                 | The E31 supports the following modes: Machine Mode, User Mode. |

**Table 2:** E31 Feature Set

# 3.1 Instruction Memory System

The instruction memory system consists of a dedicated 16 KiB 2-way set-associative instruction cache. The access latency of all blocks in the instruction memory system is one clock cycle. The instruction cache is not kept coherent with the rest of the platform memory system. Writes to instruction memory must be synchronized with the instruction fetch stream by executing a FENCE.I instruction.

The instruction cache has a line size of 32 bytes, and a cache line fill triggers a burst access. The core caches instructions from executable addresses, with the exception of the Instruction Tightly Integrated Memory (ITIM), which is further described in Section 3.1.1. See the FE310-G002 Memory Map in Chapter 4 for a description of executable address regions that are denoted by the attribute X.

Trying to execute an instruction from a non-executable address results in a synchronous trap.

#### 3.1.1 I-Cache Reconfigurability

The instruction cache can be partially reconfigured into ITIM, which occupies a fixed address range in the memory map. ITIM provides high-performance, predictable instruction delivery. Fetching an instruction from ITIM is as fast as an instruction-cache hit, with no possibility of a cache miss. ITIM can hold data as well as instructions, though loads and stores from a core to its ITIM are not as performant as loads and stores to its Data Tightly Integrated Memory (DTIM).

The instruction cache can be configured as ITIM for all ways except for 1 in units of cache lines (32 bytes). A single instruction cache way must remain an instruction cache. ITIM is allocated simply by storing to it. A store to the  $n^{th}$  byte of the ITIM memory map reallocates the first n+1 bytes of instruction cache as ITIM, rounded up to the next cache line.

ITIM is deallocated by storing zero to the first byte after the ITIM region, that is, 8 KiB after the base address of ITIM as indicated in the Memory Map in Chapter 4. The deallocated ITIM space is automatically returned to the instruction cache.

For determinism, software must clear the contents of ITIM after allocating it. It is unpredictable whether ITIM contents are preserved between deallocation and allocation.

#### 3.2 Instruction Fetch Unit

The E31 instruction fetch unit contains branch prediction hardware to improve performance of the processor core. The branch predictor comprises a 28-entry branch target buffer (BTB) which predicts the target of taken branches, a 512-entry branch history table (BHT), which predicts the direction of conditional branches, and a 6-entry return-address stack (RAS) which predicts the target of procedure returns. The branch predictor has a one-cycle latency, so that correctly predicted control-flow instructions result in no penalty. Mispredicted control-flow instructions incur a three-cycle penalty.

The E31 implements the standard Compressed (C) extension to the RISC-V architecture, which allows for 16-bit RISC-V instructions.

### 3.3 Execution Pipeline

The E31 execution unit is a single-issue, in-order pipeline. The pipeline comprises five stages: instruction fetch, instruction decode and register fetch, execute, data memory access, and register writeback.

The pipeline has a peak execution rate of one instruction per clock cycle, and is fully bypassed so that most instructions have a one-cycle result latency. There are several exceptions:

- LW has a two-cycle result latency, assuming a cache hit.

- LH, LHU, LB, and LBU have a three-cycle result latency, assuming a cache hit.

- CSR reads have a three-cycle result latency.

- MUL, MULH, MULHU, and MULHSU have a 5-cycle result latency.

- DIV, DIVU, REM, and REMU have between a 2-cycle and 33-cycle result latency, depending on the operand values.

The pipeline only interlocks on read-after-write and write-after-write hazards, so instructions may be scheduled to avoid stalls.

The E31 implements the standard Multiply (M) extension to the RISC-V architecture for integer multiplication and division. The E31 has a 8-bit per cycle hardware multiply and a 1-bit per cycle hardware divide. The multiplier can only execute one operation at a time and will block until the previous operation completes.

The hart will not abandon a Divide instruction in flight. This means if an interrupt handler tries to use a register that is the destination register of a divide instruction the pipeline stalls until the divide is complete.

Branch and jump instructions transfer control from the memory access pipeline stage. Correctly-predicted branches and jumps incur no penalty, whereas mispredicted branches and jumps incur a three-cycle penalty.

Most CSR writes result in a pipeline flush with a five-cycle penalty.

### 3.4 Data Memory System

The E31 data memory system consists of a DTIM. The access latency from a core to its own DTIM is two clock cycles for full words and three clock cycles for smaller quantities. Misaligned accesses are not supported in hardware and result in a trap to allow software emulation.

Stores are pipelined and commit on cycles where the data memory system is otherwise idle. Loads to addresses currently in the store pipeline result in a five-cycle penalty.

#### 3.5 Atomic Memory Operations

The E31 core supports the RISC-V standard Atomic (A) extension on the DTIM and the peripheral memory region. Atomic memory operations to regions that do not support them generate an access exception precisely at the core.

The load-reserved and store-conditional instructions are only supported on cached regions, hence generate an access exception on DTIM and other uncached memory regions.

See *The RISC-V Instruction Set Manual, Volume I: User-Level ISA, Version 2.1* for more information on the instructions added by this extension.

### 3.6 Supported Modes

The E31 supports RISC-V user mode, providing two levels of privilege: machine (M) and user (U). U-mode provides a mechanism to isolate application processes from each other and from trusted code running in M-mode.

See *The RISC-V Instruction Set Manual, Volume II: Privileged Architecture, Version 1.10* for more information on the privilege modes.

# 3.7 Physical Memory Protection (PMP)

The E31 includes a Physical Memory Protection (PMP) unit compliant with *The RISC-V Instruction Set Manual, Volume II: Privileged Architecture, Version 1.10.* PMP can be used to set memory access privileges (read, write, execute) for specified memory regions. The E31 PMP supports 8 regions with a minimum region size of 4 bytes.

This section describes how PMP concepts in the RISC-V architecture apply to the E31. The definitive resource for information about the RISC-V PMP is *The RISC-V Instruction Set Manual, Volume II: Privileged Architecture, Version 1.10.*

#### 3.7.1 Functional Description

The E31 includes a PMP unit, which can be used to restrict access to memory and isolate processes from each other.

The E31 PMP unit has 8 regions and a minimum granularity of 4 bytes. Overlapping regions are permitted. The E31 PMP unit implements the architecturally defined pmpcfgX CSRs pmpcfg0 and pmpcfg1 supporting 8 regions. pmpcfg2 and pmpcfg3 are implemented but hardwired to zero.

The PMP registers may only be programmed in M-mode. Ordinarily, the PMP unit enforces permissions on U-mode accesses. However, locked regions (see Section 3.7.2) additionally enforce their permissions on M-mode.

#### 3.7.2 Region Locking

The PMP allows for region locking whereby, once a region is locked, further writes to the configuration and address registers are ignored. Locked PMP entries may only be unlocked with a system reset. A region may be locked by setting the L bit in the pmpicfg register.

In addition to locking the PMP entry, the L bit indicates whether the R/W/X permissions are enforced on M-Mode accesses. When the L bit is clear, the R/W/X permissions apply only to U-mode.

#### 3.8 Hardware Performance Monitor

The FE310-G002 supports a basic hardware performance monitoring facility compliant with *The RISC-V Instruction Set Manual, Volume II: Privileged Architecture, Version 1.10.* The mcycle CSR holds a count of the number of clock cycles the hart has executed since some arbitrary time in the past. The minstret CSR holds a count of the number of instructions the hart has retired since some arbitrary time in the past. Both are 64-bit counters. The mcycle and minstret CSRs hold the 32 least-significant bits of the corresponding counter, and the mcycleh and minstreth CSRs hold the most-significant 32 bits.

The hardware performance monitor includes two additional event counters, mhpmcounter3 and mhpmcounter4. The event selector CSRs mhpmevent3 and mhpmevent4 are registers that control which event causes the corresponding counter to increment. The mhpmcounters are 40-bit counters. The mhpmcounter\_i CSR holds the 32 least-significant bits of the corresponding counter, and the mhpmcounter\_ih CSR holds the 8 most-significant bits.

The event selectors are partitioned into two fields, as shown in Table 3: the lower 8 bits select an event class, and the upper bits form a mask of events in that class. The counter increments if the event corresponding to any set mask bit occurs. For example, if mhpmevent3 is set to 0x4200, then mhpmcounter3 will increment when either a load instruction or a conditional branch instruction retires. An event selector of 0 means "count nothing."

Note that in-flight and recently retired instructions may or may not be reflected when reading or writing the performance counters or writing the event selectors.

| Machine Ha                             | ardware Performance Monitor Event Register                                                                                                                                                                                                              |

|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ins                                    | truction Commit Events, mhpeventX[7:0] = 0                                                                                                                                                                                                              |

| Bits                                   | Meaning                                                                                                                                                                                                                                                 |

| 8                                      | Exception taken                                                                                                                                                                                                                                         |

| 9                                      | Integer load instruction retired                                                                                                                                                                                                                        |

| 10                                     | Integer store instruction retired                                                                                                                                                                                                                       |

| 11                                     | Atomic memory operation retired                                                                                                                                                                                                                         |

| 12                                     | System instruction retired                                                                                                                                                                                                                              |

| 13                                     | Integer arithmetic instruction retired                                                                                                                                                                                                                  |

| 14                                     | Conditional branch retired                                                                                                                                                                                                                              |

| 15                                     | JAL instruction retired                                                                                                                                                                                                                                 |

| 16                                     | JALR instruction retired                                                                                                                                                                                                                                |

| 17                                     | Integer multiplication instruction retired                                                                                                                                                                                                              |

| 18                                     | Integer division instruction retired                                                                                                                                                                                                                    |

| Mic                                    | croarchitectural Events, mhpevent $X[7:0] = 1$                                                                                                                                                                                                          |

| Bits                                   | Meaning                                                                                                                                                                                                                                                 |

| 8                                      | Load-use interlock                                                                                                                                                                                                                                      |

| 9                                      | Long-latency interlock                                                                                                                                                                                                                                  |

|                                        |                                                                                                                                                                                                                                                         |

| 10                                     | CSR read interlock                                                                                                                                                                                                                                      |

| 10<br>11                               | CSR read interlock Instruction cache/ITIM busy                                                                                                                                                                                                          |

|                                        | Instruction cache/ITIM busy Data cache/DTIM busy                                                                                                                                                                                                        |

| 11                                     | Instruction cache/ITIM busy                                                                                                                                                                                                                             |

| 11<br>12                               | Instruction cache/ITIM busy Data cache/DTIM busy                                                                                                                                                                                                        |

| 11<br>12<br>13                         | Instruction cache/ITIM busy Data cache/DTIM busy Branch direction misprediction Branch/jump target misprediction Pipeline flush from CSR write                                                                                                          |

| 11<br>12<br>13<br>14                   | Instruction cache/ITIM busy Data cache/DTIM busy Branch direction misprediction Branch/jump target misprediction                                                                                                                                        |

| 11<br>12<br>13<br>14<br>15             | Instruction cache/ITIM busy Data cache/DTIM busy Branch direction misprediction Branch/jump target misprediction Pipeline flush from CSR write                                                                                                          |

| 11<br>12<br>13<br>14<br>15<br>16<br>17 | Instruction cache/ITIM busy Data cache/DTIM busy Branch direction misprediction Branch/jump target misprediction Pipeline flush from CSR write Pipeline flush from other event                                                                          |

| 11<br>12<br>13<br>14<br>15<br>16<br>17 | Instruction cache/ITIM busy Data cache/DTIM busy Branch direction misprediction Branch/jump target misprediction Pipeline flush from CSR write Pipeline flush from other event Integer multiplication interlock                                         |

| 11<br>12<br>13<br>14<br>15<br>16<br>17 | Instruction cache/ITIM busy Data cache/DTIM busy Branch direction misprediction Branch/jump target misprediction Pipeline flush from CSR write Pipeline flush from other event Integer multiplication interlock emory System Events, mhpeventX[7:0] = 2 |

Table 3:

mhpmevent Register Description

# **Memory Map**

The memory map of the FE310-G002 is shown in Table 4.

| Base        | Тор         | Attr. | Description       | Notes                             |  |

|-------------|-------------|-------|-------------------|-----------------------------------|--|

| 0×0000_0000 | 0x0000_0FFF | RWX A | Debug             | Debug Address Space               |  |

| 0×0000_1000 | 0x0000_1FFF | R XC  | Mode Select       |                                   |  |

| 0x0000_2000 | 0x0000_2FFF |       | Reserved          |                                   |  |

| 0×0000_3000 | 0x0000_3FFF | RWX A | Error Device      |                                   |  |

| 0x0000_4000 | 0x0000_FFFF |       | Reserved          | On-Chip Non Volatile Mem-         |  |

| 0×0001_0000 | 0x0001_1FFF | R XC  | Mask ROM (8 KiB)  | ory                               |  |

| 0x0001_2000 | 0x0001_FFFF |       | Reserved          |                                   |  |

| 0x0002_0000 | 0x0002_1FFF | R XC  | OTP Memory Region |                                   |  |

| 0x0002_2000 | 0x001F_FFFF |       | Reserved          |                                   |  |

| 0x0200_0000 | 0x0200_FFFF | RW A  | CLINT             |                                   |  |

| 0x0201_0000 | 0x07FF_FFFF |       | Reserved          |                                   |  |

| 0x0800_0000 | 0x0800_1FFF | RWX A | E31 ITIM (8 KiB)  |                                   |  |

| 0x0800_2000 | 0x0BFF_FFFF |       | Reserved          |                                   |  |

| 0x0C00_0000 | 0x0FFF_FFFF | RW A  | PLIC              |                                   |  |

| 0×1000_0000 | 0x1000_0FFF | RW A  | AON               |                                   |  |

| 0x1000_1000 | 0x1000_7FFF |       | Reserved          |                                   |  |

| 0x1000_8000 | 0x1000_8FFF | RW A  | PRCI              |                                   |  |

| 0x1000_9000 | 0x1000_FFFF |       | Reserved          |                                   |  |

| 0x1001_0000 | 0x1001_0FFF | RW A  | OTP Control       |                                   |  |

| 0×1001_1000 | 0x1001_1FFF |       | Reserved          |                                   |  |

| 0x1001_2000 | 0x1001_2FFF | RW A  | GPIO              | On-Chip Peripherals               |  |

| 0x1001_3000 | 0x1001_3FFF | RW A  | UART 0            | On-Chip Peripherais               |  |

| 0x1001_4000 | 0x1001_4FFF | RW A  | QSPI 0            |                                   |  |

| 0x1001_5000 | 0x1001_5FFF | RW A  | PWM 0             |                                   |  |

| 0x1001_6000 | 0x1001_6FFF | RW A  | I2C 0             |                                   |  |

| 0x1001_7000 | 0x1002_2FFF |       | Reserved          |                                   |  |

| 0x1002_3000 | 0x1002_3FFF | RW A  | UART 1            |                                   |  |

| 0×1002_4000 | 0x1002_4FFF | RW A  | SPI 1             |                                   |  |

| 0x1002_5000 | 0x1002_5FFF | RW A  | PWM 1             |                                   |  |

| 0x1002_6000 | 0x1003_3FFF |       | Reserved          |                                   |  |

| 0x1003_4000 | 0x1003_4FFF | RW A  | SPI 2             |                                   |  |

| 0x1003_5000 | 0x1003_5FFF | RW A  | PWM 2             |                                   |  |

| 0x1003_6000 | 0x1FFF_FFFF |       | Reserved          |                                   |  |

| 0x2000_0000 | 0x3FFF_FFFF | R XC  | QSPI 0 Flash      | Off-Chin Non-Volatile Mom         |  |

|             |             |       | (512 MiB)         | Off-Chip Non-Volatile Mem-<br>ory |  |

| 0x4000_0000 | 0x7FFF_FFFF |       | Reserved          | 01 y                              |  |

| 0x8000_0000 | 0x8000_3FFF | RWX A | E31 DTIM (16 KiB) | On-Chip Volatile Memory           |  |

| 0x8000_4000 | 0xFFFF_FFFF |       | Reserved          | Cit of the volume internety       |  |

**Table 4:** FE310-G002 Memory Map. Memory Attributes: **R** - Read, **W** - Write, **X** - Execute, **C** - Cacheable, **A** - Atomics

# **Boot Process**

The FE310-G002 supports booting from several sources, which are controlled using the Mode Select (MSEL[1:0]) pins on the chip. All possible values are enumerated in Table 5.

| MSEL | Purpose                                                    |

|------|------------------------------------------------------------|

| 00   | loops forever waiting for debugger                         |

| 01   | jump directly to 0x2000_0000 (memory-mapped QSPI0)         |

| 10   | jump directly to 0x0002_0000 (OTP)                         |

| 11   | jump directly to 0x0001_0000 (Mask ROM: Default Boot Mode) |

Table 5: Boot media based on MSEL pins

#### 5.1 Reset Vector

On power-on, the core's reset vector is 0x1004.

| Address | Contents           |  |

|---------|--------------------|--|

| 0x1000  | The MSEL pin state |  |

| 0x1004  | auipc t0, 0        |  |

| 0x1008  | lw t1, -4(t0)      |  |

| 0x100C  | slli t1, t1, 0x3   |  |

| 0x1010  | add t0, t0, t1     |  |

| 0x1014  | lw t0, 252(t0)     |  |

| 0x1018  | jr t0              |  |

Table 6: Reset vector ROM

This small gate ROM implements an MSEL-dependent jump for all cores as follows:

| MSEL | Reset address | Purpose                               |

|------|---------------|---------------------------------------|

| 00   | 0x0000_1004   | loops forever waiting for debugger    |

| 01   | 0x2000_0000   | memory-mapped QSPI0                   |

| 10   | 0x0002_0000   | memory-mapped OTP                     |

| 11   | 0x0001_0000   | memory-mapped Mask ROM (jumps to OTP) |

**Table 7:** Target of the reset vector

#### 5.1.1 Mask ROM (MROM)

MROM is fixed at design time, and is located on the peripheral bus on FE310-G002, but instructions fetched from MROM are cached by the core's I-cache. The MROM contains an instruction at address 0x1\_0000 which jumps to the OTP start address at 0x2\_0000.

#### 5.1.2 One-Time Programmable (OTP) Memory

The OTP is located on the peripheral bus, with both a control register interface to program the OTP, and a memory read port interface to fetch words from the OTP. Instruction fetches from the OTP memory read port are cached in the E31 core's instruction cache.

The OTP needs to be programmed before use and can only be programmed by code running on the core. The OTP bits contain all 0s prior to programming.

#### 5.1.3 Quad SPI Flash Controller (QSPI)

The dedicated QSPI flash controller connects to external SPI flash devices that are used for execute-in-place code. SPI flash is not available in certain scenarios such as package testing or board designs not using SPI flash (e.g., just using on-chip OTP).

Off-chip SPI devices can vary in number of supported I/O bits (1, 2, or 4). SPI flash bits contain all 1s prior to programming.

# **Clock Generation**

The FE310-G002 supports many alternative clock-generation schemes to match application needs. This chapter describes the structure of the clock generation system. The various clock configuration registers live either in the AON block (Chapter 13) or the PRCI block (Section 6.2).

#### 6.1 Clock Generation Overview

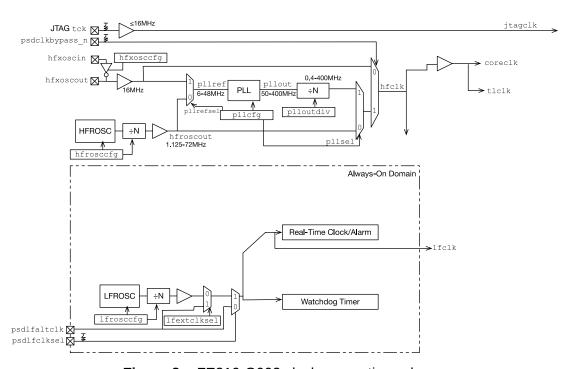

Figure 2: FE310-G002 clock generation scheme

Figure 2 shows an overview of the FE310-G002 clock generation scheme. Most digital clocks on the chip are divided down from a central high-frequency clock hfclk produced from either the PLL or an on-chip trimmable oscillator. The PLL can be driven from either the on-chip oscil-

lator or an off-chip crystal oscillator. The off-chip oscillator can also drive the high-frequency clock directly.

For the FE310-G002, the TileLink bus clock (tlclk) is fixed to be the same as the processor core clock (coreclk).

The Always-On block includes a real-time clock circuit that is driven from one of the low-frequency clock sources: an off-chip oscillator (LFOSC) or an an on-chip low-frequency oscillator (LFROSC).

### 6.2 PRCI Address Space Usage

PRCI (Power, Reset, Clock, Interrupt) is an umbrella term for platform non-AON memory-mapped control and status registers controlling component power states, resets, clock selection, and low-level interrupts, hence the name. The PRCI registers are generally only made visible to machine-mode software. The AON block contains registers with similar functions, but only for the AON block units.

| Table 8 shows the memory man    | for the PRCI on the FE310-G002. |

|---------------------------------|---------------------------------|

| Table 6 SHOWS the Inclinity map |                                 |

| Offset | Name       | Description                                 |

|--------|------------|---------------------------------------------|

| 0×00   | hfrosccfg  | Ring Oscillator Configuration and Status    |

| 0x04   | hfxosccfg  | Crystal Oscillator Configuration and Status |

| 0x08   | pllcfg     | PLL Configuration and Status                |

| 0x0C   | plloutdiv  | PLL Final Divide Configuration              |

| 0xF0   | procmoncfg | Process Monitor Configuration and Status    |

**Table 8:** SiFive PRCI memory map, offsets relative to PRCI base address.

# **6.3** Internal Trimmable Programmable 72 MHz Oscillator (HFROSC)

An internal trimmable high-frequency ring oscillator (HFROSC) is used to provide the default clock after reset, and can be used to allow operation without an external high-frequency crystal or the PLL.

The oscillator is controlled by the hfrosccfg register, which is memory-mapped in the PRCI address space, and whose format is shown in Table 9.

| hfrosccfg: Ring Oscillator Configuration and Status (hfrosccfg) |            |       |      |                                  |

|-----------------------------------------------------------------|------------|-------|------|----------------------------------|

| Register Offset                                                 |            | 0×0   |      |                                  |

| Bits                                                            | Field Name | Attr. | Rst. | Description                      |

| [5:0]                                                           | hfroscdiv  | RW    | 0x4  | Ring Oscillator Divider Register |

| [15:6]                                                          | Reserved   |       |      |                                  |

| [20:16]                                                         | hfrosctrim | RW    | 0x10 | Ring Oscillator Trim Register    |

| [29:21]                                                         | Reserved   |       |      |                                  |

| 30                                                              | hfroscen   | RW    | 0x1  | Ring Oscillator Enable           |

| 31                                                              | hfroscrdy  | R0    | Х    | Ring Oscillator Ready            |

**Table 9:** hfrosccfg: Ring Oscillator Configuration and Status

The frequency can be adjusted in software using a 5-bit trim value in the hfrosctrim. The trim value (from 0–31) adjusts which tap of the variable delay chain is fed back to the start of the ring. A value of 0 corresponds to the longest chain and slowest frequency, while higher values correspond to shorter chains and therefore higher frequencies.

The HFROSC oscillator output frequency can be divided by an integer between 1 and 64 giving a frequency range of 1.125 MHz–72 MHz assuming the trim value is set to give a 72 MHz output. The value of the divider is given in the hfroscdiv field, where the divide ratio is one greater than the binary value held in the field (i.e., hfroscdiv=0 indicates divide by 1, hfroscdiv=1 indicates divide by 2, etc.). The value of the divider can be changed at any time.

The HFROSC is the default clock source used for the system core at reset. After a reset, the hfrosctrim value is reset to 16, the middle of the adjustable range, and the divider is reset to divide-by-5 (hfroscdiv=4), which gives a nominal 13.8 MHz (±50%) output frequency.

The value of hfrosctrim that most closely achieves an 72 MHz clock output at nominal conditions (1.8 V at 25 °C) is determined by manufacturing-time calibration and is stored in on-chip OTP storage. Upon reset, software in the processor boot sequence can write the calibrated value into the hfrosctrim field, but the value can be altered at any time during operation including when the processor is running from HFROSC.

To save power, the HFROSC can be disabled by clearing hfroscen. The processor must be running from a different clock source (the PLL, external crystal, or external clock) before disabling HFROSC. HFROSC can be explicitly renabled by setting hfroscen. HFROSC will be automatically re-enabled at every reset.

The status bit hfroscrdy indicates if the oscillator is operational and ready for use as a clock source.

### 6.4 External 16 MHz Crystal Oscillator (HFXOSC)

An external high-frequency 16 MHz crystal oscillator can be used to provide a precise clock source. The crystal oscillator should have a capacitive load of  $\leq$  12 pF and an ESR  $\leq$  80  $\Omega$ .

When used to drive the PLL, the 16 MHz crystal oscillator output frequency must be divided by two in the first-stage divider of the PLL (i.e., R=2) to provide an 8 MHz reference clock to the VCO.

The input pad of the HFXOSC can also be used to supply an external clock source, in which case, the output pad should be left unconnected.

The HFXOSC input can be used to generate hfclk directly if the PLL is set to bypass.

The HFXOSC is controlled via the memory-mapped hfxosccfg register.

| hfxosccfg: Crystal Oscillator Configuration and Status (hfxosccfg) |            |       |      |                           |

|--------------------------------------------------------------------|------------|-------|------|---------------------------|

| Registe                                                            | r Offset   | 0x4   |      |                           |

| Bits                                                               | Field Name | Attr. | Rst. | Description               |

| [29:0]                                                             | Reserved   |       |      |                           |

| 30                                                                 | hfxoscen   | RW    | 0x1  | Crystal Oscillator Enable |

| 31                                                                 | hfxoscrdy  | R0    | Х    | Crystal Oscillator Ready  |

Table 10: hfxosccfg: Crystal Oscillator Configuration and Status

The hfxoscen bit turns on the crystal driver and is set on wakeup reset, but can be cleared to turn off the crystal driver and reduce power consumption. The hfxoscrdy bit indicates if the crystal oscillator output is ready for use.

The hfxoscen bit must also be turned on to use the HFXOSC input pad to connect an external clock source.

# 6.5 Internal High-Frequency PLL (HFPLL)

The PLL generates a high-frequency clock by multiplying a mid-frequency reference source clock, either the HFROSC or the HFXOSC. The input frequency to the PLL can be in the range 6–48 MHz. The PLL can generate output clock frequencies in the range 48–384 MHz.

The PLL is controlled by a memory-mapped read-write pllcfg register in the PRCI address space. The format of pllcfg is shown in Table 11.

| pllcfg: PLL Configuration and Status (pllcfg) |                 |       |      |                      |

|-----------------------------------------------|-----------------|-------|------|----------------------|

| Registe                                       | Register Offset |       |      |                      |

| Bits                                          | Field Name      | Attr. | Rst. | Description          |

| [2:0]                                         | pllr            | RW    | 0x1  | PLL R Value          |

| 3                                             | Reserved        |       |      |                      |

| [9:4]                                         | pllf            | RW    | 0x1F | PLL F Value          |

| [11:10]                                       | pllq            | RW    | 0x3  | PLL Q Value          |

| [15:12]                                       | Reserved        |       |      |                      |

| 16                                            | pllsel          | RW    | 0x0  | PLL Select           |

| 17                                            | pllrefsel       | RW    | 0x1  | PLL Reference Select |

| 18                                            | pllbypass       | RW    | 0x1  | PLL Bypass           |

| [30:19]                                       | Reserved        |       |      |                      |

| 31                                            | plllock         | R0    | Х    | PLL Lock             |

Table 11: pllcfg: PLL Configuration and Status

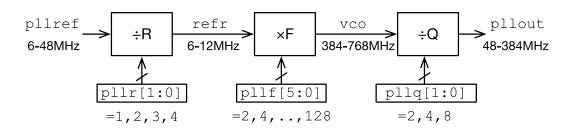

Figure 3 shows how the PLL output frequency is set using a combination of three read-write fields: pllr[2:0], pllf[2:0], pllq[1:0]. The frequency constraints must be observed between each stage for correct operation.

**Figure 3:** Controlling the FE310-G002 PLL output frequency.

The pllr[1:0] field encodes the reference clock divide ratio as a 2-bit binary value, where the value is one less than the divide ratio (i.e., 00=1, 11=4). The frequency of the output of the reference divider (refr) must lie between 6–12 MHz.

The pllf[5:0] field encodes the PLL VCO multiply ratio as a 6-bit binary value, N, signifying a divide ratio of  $2 \times (N+1)$  (i.e., 000000=2, 111111=128). The frequency of the VCO output (vco) must lie between 384–768 MHz. Table 12 summarizes the valid settings of the multiply ratio.

| refr (MHz) | Legal p11 | f multiplier | vco freque | ency (MHz) |

|------------|-----------|--------------|------------|------------|

|            | Min Max   |              | Min        | Max        |

| 6          | 64        | 128          | 384        | 768        |

| 8          | 48        | 96           | 384        | 768        |

| 10         | 39        | 76           | 390        | 760        |

| 12         | 32        | 64           | 384        | 768        |

**Table 12:** Valid PLL multiply ratios. The multiplier setting in the table is given as the actual multiply ratio; the binary value stored in pllf field should be (M/2) - 1 for a multiply ratio M.

The pllq[1:0] field encodes the PLL output divide ratio as follows, 01=2, 10=4, 11=8. The value 00 is not supported. The final output of the PLL must have a frequency that lies between 48–384 MHz.

The one-bit read-write pllbypass field in the pllcfg register turns off the PLL when written with a 1 and then pllout is driven directly by the clock indicated by pllrefsel. The other PLL registers can be configured when pllbypass is set. The agent that writes pllcfg should be running from a different clock source before disabling the PLL. The PLL is also disabled with pllbypass=1 after a wakeup reset.

The pllsel bit must be set to drive the final hfclk with the PLL output, bypassed or otherwise. When pllsel is clear, the hfroscclk directly drives hfclk. The pllsel bit is clear on wakeup reset.

The pllcfg register is reset to: bypass and power off the PLL pllbypass=1; input driven from external HFXOSC oscillator pllrefsel=1; PLL not driving system clock pllsel=0; and the PLL ratios are set to R=2, F=64, and Q=8 (pllr=01, pllf=011111, pllq=11).

The PLL provides a lock signal which is set when the PLL has achieved lock, and which can be read from the most-significant bit of the pllcfg register. The PLL requires up to 100  $\mu$ s to regain lock once enabled, and the lock signal will not necessarily be stable during this initial lock period so should only be interrogated after this period. The PLL may not achieve lock and the lock signal might not remain asserted if there is excessive jitter in the source clock.

The PLL requires dedicated 1.8 V power supply pads with a supply filter on the circuit board. The supply filter should be a 100  $\Omega$  resistor in series with the board 1.8 V supply decoupled with a 100 nF capacitor across the VDDPLL/VSSPLL supply pins. The VSSPLL pin should not be connected to board VSS.

# 6.6 PLL Output Divider

The plloutdiv register controls a clock divider that divides the output of the PLL.

| plloutdiv: PLL Final Divide Configuration (plloutdiv) |              |       |      |                         |

|-------------------------------------------------------|--------------|-------|------|-------------------------|

| Register Offset                                       |              | 0xC   |      |                         |

| Bits                                                  | Field Name   | Attr. | Rst. | Description             |

| [5:0]                                                 | plloutdiv    | RW    | 0×0  | PLL Final Divider Value |

| [7:6]                                                 | Reserved     |       |      |                         |

| [13:8]                                                | plloutdivby1 | RW    | 0x1  | PLL Final Divide By 1   |

| [31:14]                                               | Reserved     |       |      |                         |

**Table 13:** plloutdiv: PLL Final Divide Configuration

If the plloutdivby1 bit is set, the PLL output clock is passed through undivided. If plloutdivby1 is clear, the value N in plloutdiv sets the clock-divide ratio to  $2 \times (N+1)$  (between 2–128). The output divider expands the PLL output frequency range to 0.375–384 MHz.

The plloutdivby1 register is reset to divide-by-1 (plloutdivby1=1).

# 6.7 Internal Programmable Low-Frequency Ring Oscillator (LFROSC)

A second programmable ring oscillator (LFROSC) is used to provide an internal low-frequency ≈32 kHz clock source. The LFROSC can generate frequencies in the range 1.5–230 kHz (±45%).

The 1frosccfg register lives in the AON block as shown in Table 36.

At power-on reset, the LFROSC resets to selecting the middle tap (lfrosctrim=16) and  $\div$ 5 (lfroscdiv=4), resulting in an output frequency of  $\approx$ 30 kHz.

The LFROSC can be calibrated in software using a more accurate high-frequency clock source.

| Ifrosccfg: Ring Oscillator Configuration and Status (1frosccfg) |            |       |      |                                  |

|-----------------------------------------------------------------|------------|-------|------|----------------------------------|

| Register Offset                                                 |            | 0×70  |      |                                  |

| Bits                                                            | Field Name | Attr. | Rst. | Description                      |

| [5:0]                                                           | lfroscdiv  | RW    | 0x4  | Ring Oscillator Divider Register |

| [15:6]                                                          | Reserved   |       |      |                                  |

| [20:16]                                                         | lfrosctrim | RW    | 0x10 | Ring Oscillator Trim Register    |

| [29:21]                                                         | Reserved   |       |      |                                  |

| 30                                                              | lfroscen   | RW    | 0x1  | Ring Oscillator Enable           |

| 31                                                              | lfroscrdy  | R0    | Х    | Ring Oscillator Ready            |

**Table 14:** If rosccfg: Ring Oscillator Configuration and Status

# 6.8 Alternate Low-Frequency Clock (LFALTCLK)

An external low-frequency clock can be driven on the psdlfaltclk pad, when the psdlfaltclksel is tied low. This mux selection can also be controlled by software using the lfextclk\_sel in lfclkmux shown in Table 15. The current value of the psdlfaltclksel pad can be read in lfextclk\_mux\_status field.

| Ifclkmux: Low-Frequency Clock Mux Control and Status (1fc1kmux) |                     |       |      |                                     |  |  |  |  |

|-----------------------------------------------------------------|---------------------|-------|------|-------------------------------------|--|--|--|--|

| Register Offset                                                 |                     | 0x7C  |      |                                     |  |  |  |  |

| Bits                                                            | Field Name          | Attr. | Rst. | Description                         |  |  |  |  |

| 0                                                               | lfextclk_sel        | RW    | 0×0  | Low Frequency Clock Source Selector |  |  |  |  |

| [30:1]                                                          | Reserved            |       |      |                                     |  |  |  |  |

| 31                                                              | lfextclk_mux_status | R0    | Х    | Setting of the aon_lfclksel pin     |  |  |  |  |

Table 15:

Ifclkmux: Low-Frequency Clock Mux Control and Status

# 6.9 Clock Summary

Table 16 summarizes the major clocks on the FE310-G002 and their initial reset conditions. At external reset, the AON domain lfclk is clocked by either the LFROSC or psdlfaltclk, as selected by psdlfaltclksel. At wakeup reset, the MOFF domain hfclk is clocked by the HFROSC.

| Name           | Reset     |          | Notes     |         |                |  |  |  |  |

|----------------|-----------|----------|-----------|---------|----------------|--|--|--|--|

|                | Source    | Reset    | Min       | Max     |                |  |  |  |  |

| AON Domain     |           |          |           |         |                |  |  |  |  |

| LFROSC         | lfroscrst | 32 kHz   | 1.5 kHz   | 230 kHz | ±45%           |  |  |  |  |

| psdlfaltclk    | -         | -        | 0 kHz     | 500 kHz | When selected  |  |  |  |  |

|                |           |          |           |         | by             |  |  |  |  |

|                |           |          |           |         | psdlfaltclksel |  |  |  |  |

| MOFF Domain    |           |          |           |         |                |  |  |  |  |

| HFROSC         | hfclkrst  | 13.8 MHz | 0.77 MHz  | 20 MHz  | ±45%           |  |  |  |  |

| HFXOSC crystal | hfclkrst  | ON       | 10 MHz    | 20 MHz  | 16 MHz on      |  |  |  |  |

|                |           |          |           |         | HiFive         |  |  |  |  |

| HFXOSC input   | hfclkrst  | ON       | 0 MHz     | 20 MHz  | External clock |  |  |  |  |

|                |           |          |           |         | source         |  |  |  |  |

| PLL            | hfclkrst  | OFF      | 0.375 MHz | 384 MHz |                |  |  |  |  |

| JTAG TCK       | -         | OFF      | 0 MHz     | 16 MHz  |                |  |  |  |  |

Table 16: FE310-G002 Clock Sources

# **Power Modes**

This chapter describes the different power modes available on the FE310-G002. The FE310-G002 supports three power modes: Run, Wait, and Sleep.

#### 7.1 Run Mode

Run mode corresponds to regular execution where the processor is running. Power consumption can be adjusted by varying the clock frequency of the processor and peripheral bus, and by enabling or disabling individual peripheral blocks. The processor exits run mode by executing a "Wait for Interrupt" (WFI) instruction.

#### 7.2 Wait Mode