# LARA-R6/L6 series

# Single or multi-mode LTE Cat 1 / 4 modules

System integration manual

#### Abstract

This document describes the features and integration guidelines for the LARA-R6 series LTE Cat 1 single or multi-mode modules and the LARA-L6 series LTE Cat 4 multi-mode modules. These cellular modules are featuring uncompromised global connectivity in smallest form factor with secure cloud. LARA-R6 / L6 series includes various voice & data or data-only variants for different deployments, offering great flexibility and simplifying customers logistics. Comprehensive certification scheme, versatile interfaces, secure by design, feature rich and with multi-band and multi-mode capabilities make these modules suitable for use in any region and in wide range of applications.

www.u-blox.com

# **Document information**

| Title                  | LARA-R6 / L6 series                        |  |  |  |  |  |  |

|------------------------|--------------------------------------------|--|--|--|--|--|--|

| Subtitle               | Single or multi-mode LTE Cat 1 / 4 modules |  |  |  |  |  |  |

| Document type          | System integration manual                  |  |  |  |  |  |  |

| Document number        | UBX-21010011                               |  |  |  |  |  |  |

| Revision and date      | R09 28-Mar-2023                            |  |  |  |  |  |  |

| Disclosure restriction | C1-Public                                  |  |  |  |  |  |  |

| Product status                   | Corresponding content status |                                                                                        |  |  |  |  |

|----------------------------------|------------------------------|----------------------------------------------------------------------------------------|--|--|--|--|

| Functional sample                | Draft                        | For functional testing. Revised and supplementary data will be published later.        |  |  |  |  |

| In development /<br>Prototype    | Objective specification      | Target values. Revised and supplementary data will be published later.                 |  |  |  |  |

| Engineering sample               | Advance information          | Data based on early testing. Revised and supplementary data will be published later.   |  |  |  |  |

| Initial production               | Early production information | Data from product verification. Revised and supplementary data may be published later. |  |  |  |  |

| Mass production /<br>End of life | Production information       | Document contains the final product specification.                                     |  |  |  |  |

This document applies to the following products:

| Product name | Type number        | Modem version | Application version | PCN reference | Product status    |

|--------------|--------------------|---------------|---------------------|---------------|-------------------|

| LARA-R6001   | LARA-R6001-00B-00  | 02.14         | A00.01              | UBX-22019779  | End of Life       |

|              | LARA-R6001-00B-01  | 02.14         | A00.01              | UBX-23004170  | Mass production   |

|              | LARA-R6001-01B-00  | N/A           | N/A                 | N/A           | Functional sample |

| LARA-R6001D  | LARA-R6001D-00B-00 | 00.13         | A00.01              | UBX-22008409  | End of Life       |

|              | LARA-R6001D-00B-01 | 00.13         | A00.01              | UBX-23004170  | Mass production   |

|              | LARA-R6001D-01B-00 | N/A           | N/A                 | N/A           | Functional sample |

| LARA-R6401   | LARA-R6401-00B-00  | 02.14         | A00.01              | UBX-22019779  | End of Life       |

|              | LARA-R6401-00B-01  | 02.14         | A00.01              | UBX-23004170  | Mass production   |

|              | LARA-R6401-01B-00  | N/A           | N/A                 | N/A           | Functional sample |

| LARA-R6401D  | LARA-R6401D-00B-00 | 01.14         | A00.01              | UBX-22014149  | End of Life       |

|              | LARA-R6401D-00B-01 | 02.14         | A00.01              | UBX-23004170  | Mass production   |

|              | LARA-R6401D-01B-00 | N/A           | N/A                 | N/A           | Functional sample |

| LARA-R6801   | LARA-R6801-00B-00  | 02.14         | A00.01              | UBX-22019779  | End of Life       |

|              | LARA-R6801-00B-01  | 02.14         | A00.01              | UBX-22038730  | Mass production   |

|              | LARA-R6801-01B-00  | N/A           | N/A                 | N/A           | Functional sample |

| LARA-R6801D  | LARA-R6801D-01B-00 | N/A           | N/A                 | N/A           | Functional sample |

| LARA-L6004   | LARA-L6004-00B-00  | 03.16         | A00.01              | UBX-23003246  | Mass production   |

|              | LARA-L6004-01B-00  | N/A           | N/A                 | N/A           | Functional sample |

| LARA-L6004D  | LARA-L6004D-00B-00 | 03.16         | A00.01              | UBX-23003246  | Mass production   |

|              | LARA-L6004D-01B-00 | N/A           | N/A                 | N/A           | Functional sample |

| LARA-L6804D  | LARA-L6804D-01B-00 | N/A           | N/A                 | N/A           | Functional sample |

u-blox or third parties may hold intellectual property rights in the products, names, logos and designs included in this document. Copying, reproduction, modification or disclosure to third parties of this document or any part thereof is only permitted with the express written permission of u-blox.

The information contained herein is provided "as is" and u-blox assumes no liability for its use. No warranty, either express or implied, is given, including but not limited to, with respect to the accuracy, correctness, reliability and fitness for a particular purpose of the information. This document may be revised by u-blox at any time without notice. For the most recent documents, visit www.u-blox.com.

Copyright © u-blox AG.

# Contents

| Documen              | t information                                                | 2  |

|----------------------|--------------------------------------------------------------|----|

| Contents             |                                                              | 3  |

| 1 Syste              | m description                                                | 6  |

| 1.1 Ove              | rview                                                        | 6  |

| 1.2 Arcl             | hitecture                                                    | 9  |

| 1.3 Pin-             | out                                                          | 10 |

| 1.4 Ope              | rating modes                                                 | 14 |

| 1.5 Sup              | ply interfaces                                               | 15 |

| 1.5.1                | Module supply input (VCC)                                    | 15 |

| 1.5.2                | Generic digital interfaces supply output (V_INT)             | 21 |

| 1.6 Sys <sup>-</sup> | tem function interfaces                                      | 22 |

| 1.6.1                | Module power-on                                              | 22 |

| 1.6.2                | Module power-off                                             | 24 |

| 1.6.3                | Module reset                                                 | 26 |

| 1.7 Ant              | enna interfaces                                              | 27 |

| 1.7.1                | Antenna RF interfaces (ANT1 / ANT2)                          | 27 |

| 1.7.2                | Antenna detection (ANT_DET)                                  | 29 |

| 1.7.3                | Antenna dynamic tuning control interface (RFCTRL1 / RFCTRL2) | 29 |

| 1.8 SIM              | interface                                                    | 30 |

| 1.8.1                | SIM card / chip interface                                    | 30 |

| 1.8.2                | SIM card detection interface                                 | 30 |

| 1.9 Seri             | al communication interfaces                                  | 30 |

| 1.9.1                | UART interfaces                                              | 31 |

| 1.9.2                | USB interface                                                | 33 |

| 1.9.3                | I2C interface                                                | 33 |

| 1.10 Aud             | lio interface                                                | 34 |

| 1.11 Cloc            | ck output                                                    | 35 |

| 1.12Gen              | eral Purpose Input/Output (GPIO)                             | 35 |

| 1.13Res              | erved pins (RSVD)                                            | 36 |

| 2 Desig              | n-in                                                         |    |

| 2.1 Ove              | rview                                                        |    |

| 2.2 Sup              | ply interfaces                                               |    |

| 2.2.1                | Module supply (VCC)                                          |    |

| 2.2.2                | Interface supply (V_INT)                                     | 52 |

| 2.3 Sys <sup>.</sup> | tem functions interfaces                                     |    |

| 2.3.1                | Module power-on (PWR_ON)                                     | 53 |

| 2.3.2                | Module reset (RESET_N)                                       |    |

| 2.4 Ant              | enna interfaces                                              |    |

| 2.4.1                | Antenna RF interface (ANT1 / ANT2)                           |    |

| 2.4.2                | Antenna detection interface (ANT_DET)                        | 63 |

| 2.4.3      | Antenna dynamic tuning control interface (RFCTRL1 / RFCTRL2) | 65 |

|------------|--------------------------------------------------------------|----|

| 2.5 SIM i  | nterface                                                     | 67 |

| 2.6 Seria  | l communication interfaces                                   | 73 |

| 2.6.1      | UART interfaces                                              | 73 |

| 2.6.2      | USB interface                                                | 79 |

| 2.6.3      | I2C interface                                                | 81 |

| 2.7 Audio  | o interface                                                  | 84 |

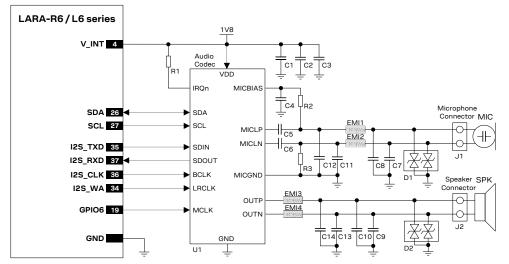

| 2.7.1      | Digital audio interface                                      | 84 |

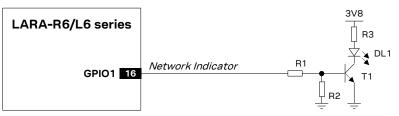

| 2.8 Gene   | ral Purpose Input/Output (GPIO)                              | 87 |

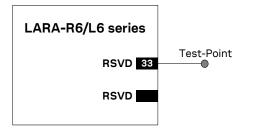

| 2.9 Rese   | rved pins (RSVD)                                             | 88 |

| 2.10 Modu  | ule placement                                                | 88 |

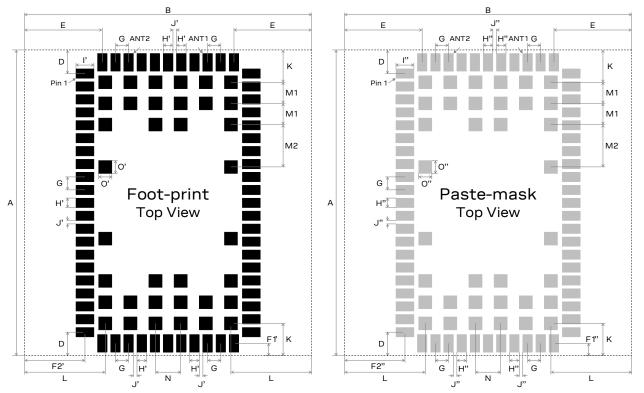

|            | le footprint and paste mask                                  |    |

| 2.12 Ther  | mal guidelines                                               | 90 |

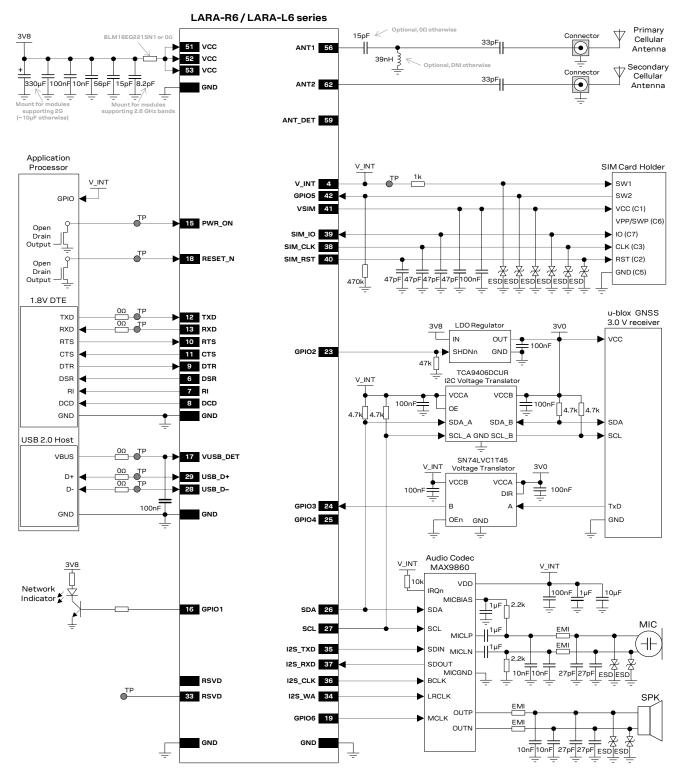

|            | matic for LARA-R6 / L6 series module integration             |    |

| 2.14 Desię | gn-in checklist                                              | 92 |

| 2.14.1     | Schematic checklist                                          | 92 |

| 2.14.2     | Layout checklist                                             | 92 |

| 2.14.3     | Antenna checklist                                            | 93 |

| 3 Handli   | ng and soldering                                             |    |

| 3.1 Pack   | aging, shipping, storage and moisture preconditioning        | 94 |

| 3.2 Hand   | lling                                                        | 94 |

| 3.3 Solde  | ering                                                        | 95 |

| 3.3.1      | Soldering paste                                              | 95 |

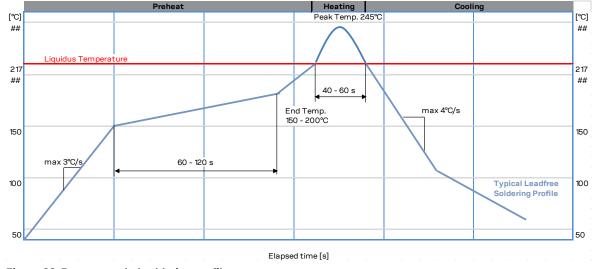

| 3.3.2      | Reflow soldering                                             | 95 |

| 3.3.3      | Optical inspection                                           | 96 |

| 3.3.4      | Cleaning                                                     | 96 |

| 3.3.5      | Repeated reflow soldering                                    | 97 |

| 3.3.6      | Wave soldering                                               | 97 |

| 3.3.7      | Hand soldering                                               | 97 |

| 3.3.8      | Rework                                                       | 97 |

| 3.3.9      | Conformal coating                                            | 97 |

| 3.3.10     | Casting                                                      | 97 |

| 3.3.11     | Grounding metal covers                                       |    |

| 3.3.12     | Use of ultrasonic processes                                  |    |

| 4 Approv   | /als                                                         |    |

| 4.1 Prod   | uct certification approval overview                          | 99 |

| 4.2 US F   | ederal Communications Commission notice                      |    |

| 4.2.1      | Safety warnings review the structure                         |    |

| 4.2.2      | Declaration of conformity                                    |    |

| 4.2.3      | Modifications                                                |    |

| 4.3 Innov  | vation, Science, Economic Development Canada notice          |    |

| 4.3.1      | Declaration of Conformity                                    |    |

| 4.3.2 Modifications                                    |  |

|--------------------------------------------------------|--|

| 4.4 European Conformance CE mark                       |  |

| 4.5 UK Conformity Assessed (UKCA)                      |  |

| 4.6 Australian conformance                             |  |

| 4.7 GITEKI Japan                                       |  |

| 4.8 National Communication Commission Taiwan           |  |

| 4.9 Korean Certification                               |  |

| 4.10 ANATEL Brazil                                     |  |

| 5 Product testing                                      |  |

| 5.1 Validation testing and qualification               |  |

| 5.2 Production testing                                 |  |

| 5.2.1 u-blox in-line production test                   |  |

| 5.2.2 Production test parameters for OEM manufacturers |  |

| Appendix                                               |  |

| A Migration from LARA-R2 to LARA-R6 / L6               |  |

| B Glossary                                             |  |

| Related documentation                                  |  |

| Revision history                                       |  |

| contact                                                |  |

# 1 System description

## 1.1 Overview

The LARA-R6 series comprises multi-band and multi-mode modules supporting LTE Cat 1 FDD and LTE Cat 1 TDD radio access technology, with 3G UMTS/HSPA and 2G GSM/GPRS/EGPRS fallback. The modules provide the ideal solution for global and multi-regional coverage in the small LARA LGA form-factor (26.0 x 24.0 mm, 100-pin), and are easy to integrate in compact designs.

LARA-R6 series comprises six variants, offering great flexibility so that customers can maximize reusing development efforts, and simplify logistics:

- LARA-R6001 (data and voice) and LARA-R6001D (data-only) modules designed for world-wide operation, supporting eighteen LTE Cat 1 FDD / TDD bands, four 3G bands and four 2G bands for global coverage

- LARA-R6401 (data and voice) and LARA-R6401D (data-only) modules designed mainly for operation in America, supporting eight LTE Cat 1 FDD bands

- LARA-R6801 (data and voice) and LARA-R6801D (data-only) modules designed for multi-regional operation, in EMEA, APAC, Japan and Latin America, supporting twelve LTE Cat 1 bands, four 3G bands and four 2G bands

Customers of LARA-R6 series modules can take advantage of the embedded IoT protocols (LwM2M, MQTT) and the embedded security features (TLS/DTLS, secure update/secure boot) to implement various applications, such as device management, remote device actions, and secure FOTA updates.

The LARA-L6 series comprises multi-band and multi-mode modules supporting LTE Cat 4 FDD and LTE Cat 4 TDD radio access technology, with 3G UMTS/HSPA and 2G GSM/GPRS/EGPRS fallback.

The LARA-L6 modules are pin-to-pin compatible with LARA-R6 modules, with the same small LARA LGA form-factor and with the same electrical characteristics in all available interfaces, except the support of the LTE Cat 4 instead of the LTE Cat 1 radio access technology. The designed pin-to-pin compatibility allows seamless migration from any LARA-R6 and/or LARA-L6 module product version.

LARA-L6 series comprises three variants, both with global coverage, simplifying customers logistics:

- LARA-L6004 (data and voice) and LARA-L6004D (data-only) modules designed for world-wide operation, supporting eighteen LTE Cat 4 FDD / TDD bands plus four 3G bands and four 2G bands for global coverage

- LARA-L6804D (data-only) module designed for multi-regional operation, in EMEA, APAC, Japan and Latin America, supporting twelve LTE Cat 4 bands, four 3G bands and four 2G bands

Versatile interfaces, features, multi-band and multi-mode capabilities make the LARA-R6 / L6 series modules ideally suited to a wide range of applications, such as asset tracking, telematics, remote monitoring, alarm panels, video surveillance, connected health, point of sale terminal, and mobile cameras. Generally, the modules are suited to applications that require medium-speed data, seamless connectivity, superior coverage, low latency, streaming services (data or voice), and to industrial applications focused on product life-cycle longevity.

#### Table 1 summarizes the main features and interfaces of the LARA-R6 / L6 series modules.

| Model       | Region           | Radio Access Technology 0                                                                     | GNSS                                                      | u-blox<br>services                                                                           | Interfaces Features                              |                                                                                                                                                                                                                                                                                                                                                                | Grade                                  |

|-------------|------------------|-----------------------------------------------------------------------------------------------|-----------------------------------------------------------|----------------------------------------------------------------------------------------------|--------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

|             |                  | LTE Category<br>LTE FDD bands<br>LTE TDD bands<br>UMTS/HSPA FDD bands<br>GSM/GPRS/EGPRS bands | Internal GNSS receiver<br>External GNSS control via modem | IoT Security -as-a-Service<br>MQTT Anywhere / MQTT Flex<br>AssistNow software<br>CellLocate® | UART<br>USB 2.0<br>I2C<br>GPIOs<br>Digital audio | Root of Trust<br>Secure boot / update<br>Embedded MQTT / MQTT-SN<br>TCP/IP, UDP/IP, HTTP/FTP<br>TSL/DTLS<br>Dual stack IPv4 / IPv6<br>FOAT / uFOTA<br>LwM2M<br>aGPP Power Saving Mode<br>eDRX<br>Last gasp<br>eDRX<br>Last gasp<br>Last gasp<br>aftenna and SIM detection<br>Antenna ad SIM detection<br>Antenna dynamic tuning<br>Rx Diversity<br>VoL TE/CSFB | Standard<br>Professional<br>Automotive |

| LARA-R6001  | Global           | 1,2,3,4,5,7,8<br>1 12,13,18,19<br>20,26,28<br>38,39 1,2<br>40,41 5,8<br>Quad                  | •                                                         | • • • •                                                                                      | 2119•                                            |                                                                                                                                                                                                                                                                                                                                                                | •                                      |

| LARA-R6001D | Global           | 1,2,3,4,5,7,8<br>1 12,13,18,19<br>20,26,28<br>38,39 1,2<br>40,41 5,8<br>Quad                  | •                                                         | ••••                                                                                         | 2119                                             |                                                                                                                                                                                                                                                                                                                                                                | •                                      |

| LARA-R6401  | North<br>America | 2,4,5<br>1 12,13,14<br>66,71                                                                  | •                                                         | • • • •                                                                                      | 2119•                                            | • • • • • • • • • • • • • • • •                                                                                                                                                                                                                                                                                                                                | •                                      |

| LARA-R6401D | North<br>America | 2,4,5<br>1 12,13,14<br>66,71                                                                  | •                                                         | • • • •                                                                                      | 2119                                             |                                                                                                                                                                                                                                                                                                                                                                | •                                      |

| LARA-R6801  | Multi-<br>Region | 1,2,3,4,5,7,8<br>1 18,19 1,2<br>20,26,28 5,8 Quad                                             | •                                                         | ••••                                                                                         | 2119•                                            |                                                                                                                                                                                                                                                                                                                                                                | •                                      |

| LARA-R6801D | Multi-<br>Region | 1,2,3,4,5,7,8<br>1 18,19 1,2<br>20,26,28 5,8 Quad                                             | •                                                         | • • • •                                                                                      | 2119                                             | •••••                                                                                                                                                                                                                                                                                                                                                          | •                                      |

| LARA-L6004  | Global           | 1,2,3,4,5,7,8<br>4 12,13,18,19<br>20,26,28<br>38,39 1,2<br>40,41 5,8<br>Quad                  | •                                                         | ••                                                                                           | 2119•                                            | • •••                                                                                                                                                                                                                                                                                                                                                          | •                                      |

| LARA-L6004D | Global           | 1,2,3,4,5,7,8<br>4 12,13,18,19<br>20,26,28<br>38,39 1,2<br>40,41 5,8 Quad                     | •                                                         | ••                                                                                           | 2119                                             | • ••••••                                                                                                                                                                                                                                                                                                                                                       | •                                      |

| LARA-L6804D | Multi-<br>Region | 1,2,3,4,5,7,8<br>4 18,19 1,2<br>20,26,28 5,8 Quad                                             | •                                                         | • •                                                                                          | 2119                                             |                                                                                                                                                                                                                                                                                                                                                                | •                                      |

• = "00B", "01B" and future product versions

= "01B" and future product versions Table 1: LARA-R6 / L6 series main features summary

T

LARA-R6001D, LARA-R6401D, LARA-R6801D and LARA-L6004D data-only modules have the same electrical characteristics, feature set and functionalities of the LARA-R6001, LARA-R6401, LARA-R6801 and LARA-L6004 data and voice modules respectively, except for the support of voice / audio. Unless otherwise specified in this document,

- "LARA-R6001" refers to both LARA-R6001 and LARA-R6001D modules. 0

- "LARA-R6401" refers to both LARA-R6401 and LARA-R6401D modules, 0

- "LARA-R6801" refers to both LARA-R6801 and LARA-R6801D modules, 0

- "LARA-L6004" refers to both LARA-L6004 and LARA-L6004D modules. 0

Except for the LARA-R6001D, LARA-R6401D, LARA-R6801D, LARA-L6004D and LARA-L6804D data-only modules, the LARA-R6 / L6 series modules provide Voice over LTE (VoLTE) and Circuit-switched fallback (CSFB)<sup>1</sup> audio capability. The 911 and E911 services are not supported.

Table 2 summarizes cellular radio access technology characteristics of LARA-R6/L6 series modules.

| 4G LTE                                                                                                                                                                                                      | 3G UMTS/HSDPA/HSUPA <sup>2</sup>                                                                                                                                                                    | 2G GSM/GPRS/EDGE <sup>3</sup>                                                                                                                                                                                                       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3GPP Release 10<br>Long Term Evolution (LTE)<br>Evolved UTRA (E-UTRA)<br>Frequency Division Duplex (FDD)<br>Time Division Duplex (TDD) <sup>4</sup><br>DL Rx diversity<br>DL MIMO 2x2 (LARA-L6 series only) | 3GPP Release 8 (LARA-R6 series)<br>3GPP Release 9 (LARA-L6 series)<br>High Speed Packet Access (HSPA)<br>UMTS Terrestrial Radio Access (UTRA)<br>Frequency Division Duplex (FDD)<br>DL Rx diversity | 3GPP Release 9<br>Enhanced Data rate GSM Evolution (EDGE)<br>GSM EGPRS Radio Access (GERA)<br>Time Division Multiple Access (TDMA)<br>DL Advanced Rx Performance Phase 1                                                            |

| LTE Power Class<br>• Power Class 3 (23 dBm)                                                                                                                                                                 | UMTS/HSDPA/HSUPA Power Class <ul> <li>Class 3 (24 dBm)</li> </ul>                                                                                                                                   | GSM/GPRS (GMSK) Power Class<br>Class 4 (33 dBm) for 850/900 band<br>Class 1 (30 dBm) for 1800/1900 band<br>EDGE (8-PSK) Power Class<br>Class E2 (27 dBm) for 850/900 band<br>Class E2 (26 dBm) for 1800/1900 band                   |

| <ul> <li>Data rate (LARA-R6 series)</li> <li>LTE category 1:<br/>up to 10.3 Mbit/s DL,<br/>up to 5.2 Mbit/s UL</li> </ul>                                                                                   | <ul> <li>Data rate (LARA-R6 series)</li> <li>HSDPA category 8:<br/>up to 7.2 Mbit/s DL</li> <li>HSUPA category 6:<br/>up to 5.76 Mbit/s UL</li> </ul>                                               | <ul> <li>Data rate<sup>5</sup></li> <li>GPRS multi-slot class 33<sup>6</sup>, CS1-CS4, up to 107 kbit/s DL, 85.6 kbit/s UL</li> <li>EDGE multi-slot class 33<sup>6</sup>, MCS1-MCS9 up to 296 kbit/s DL, 236.8 kbit/s UL</li> </ul> |

| <ul> <li>Data rate (LARA-L6 series)</li> <li>LTE category 4:<br/>up to 150 Mbit/s DL,<br/>up to 50 Mbit/s UL</li> </ul>                                                                                     | <ul> <li>Data rate (LARA-L6 series)</li> <li>HSDPA category 24:<br/>up to 42.2 Mbit/s DL</li> <li>HSUPA category 6:<br/>up to 5.76 Mbit/s UL</li> </ul>                                             |                                                                                                                                                                                                                                     |

Table 2: LARA-R6 / L6 series LTE, 3G and 2G characteristics

<sup>&</sup>lt;sup>1</sup> Circuit-Switched-Fall-Back (CSFB) is not supported by LARA-R6401 modules.

<sup>&</sup>lt;sup>2</sup> 3G radio access technology is not supported by LARA-R6401 modules.

<sup>&</sup>lt;sup>3</sup> 2G radio access technology is not supported by LARA-R6401 modules.

<sup>&</sup>lt;sup>4</sup> LTE TDD radio access technology is not supported by LARA-R6401, or LARA-R6801 modules.

<sup>&</sup>lt;sup>5</sup> GPRS/EDGE multislot class determines the number of timeslots available for upload and download and thus the speed at which data can be transmitted and received, with higher classes typically allowing faster data transfer rates.

<sup>&</sup>lt;sup>6</sup> GPRS/EDGE multislot class 33 implies a maximum of 5 slots in DL (reception), 4 slots in UL (transmission) with 6 slots in total.

## 1.2 Architecture

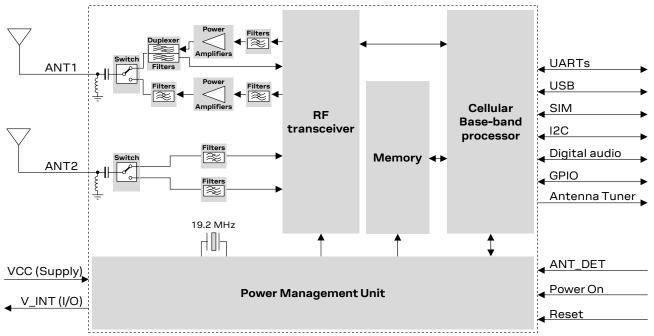

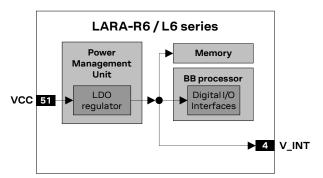

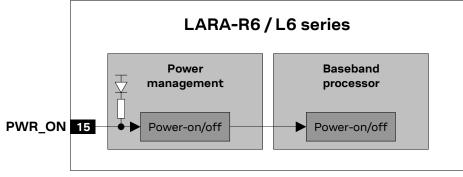

Figure 1 summarizes the internal architecture of the LARA-R6 / L6 series modules.

Figure 1: LARA-R6 / L6 series modules simplified block diagram

LARA-R6/L6 series modules internally consist of the RF, baseband and power management sections described herein with more details than the simplified block diagrams of Figure 1.

#### **RF** section

The RF section is composed of the following main elements:

- RF transceiver performs modulation, up-conversion of the baseband signals for transmission, down-conversion and demodulation of the dual RF signals for reception

- Power amplifiers (PA) amplify the Tx signal modulated by the RF transceiver

- RF switches connect primary (ANT1) and secondary (ANT2) ports to the suitable Tx / Rx path

- SAW RF duplexers and RF filters separate the Tx and Rx signal paths and provide RF filtering

- 19.2 MHz crystal oscillator generates the clock reference in active mode or connected mode.

#### Baseband and power management section

The baseband and power management section is composed of the following main elements:

- Baseband processor IC, integrating:

- Microprocessor and DSP for control functions and digital processing

- Memory interface controller

- Dedicated peripheral blocks for control of the USB, SIM and generic digital interfaces

- $_{\circ}$  Interfaces to RF transceiver ASIC

- Memory system, which includes NAND flash and LPDDR2 RAM

- Power management IC, integrating:

- Voltage regulators to derive all the internal supply voltages from VCC module supply input

- $_{\circ}$   $\,$  Voltage sources for external use: VSIM and V\_INT  $\,$

- $_{\circ}$  Hardware power on / off

- Low power modes support

## 1.3 Pin-out

Table 3 lists the pin-out of the LARA-R6 / L6 series modules, with pins grouped by function.

| Function | Pin name | Pin no.                                                               | I/O | Description                                    | Remarks                                                                                                                                                                                                                                                                                                       |

|----------|----------|-----------------------------------------------------------------------|-----|------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power    | VCC      | 51,52,53                                                              | I   | Module supply input                            | VCC supply circuit affects the RF performance and<br>compliance of the device integrating the module with<br>applicable required certification schemes.<br>See section 1.5.1 for description and requirements.<br>See section 2.2.1 for external circuit design-in.                                           |

|          | GND      | 1,3,5,14,20,<br>21,22,30,32,<br>43,50,54,55,<br>57,58,60,61,<br>63-96 | N/A | Ground                                         | GND pins are internally connected to each other.<br>External ground connection affects the RF and thermal<br>performance of the device.<br>See section 1.5.1 for functional description.<br>See section 2.2.1 for external circuit design-in.                                                                 |

|          | V_INT    | 4                                                                     | 0   | Generic Digital<br>Interfaces supply<br>output | V_INT = 1.8 V (typ.), generated by internal linear regulator<br>when the module is switched on.<br>Test-Point for diagnostic access is recommended.<br>See section 1.5.2 for functional description.<br>See section 2.2.2 for external circuit design-in.                                                     |

| System   | PWR_ON   | 15                                                                    | I   | Power-on input                                 | Internal pull-up to internal voltage domain.<br>Test-Point for diagnostic access is recommended.<br>See section 1.6.1 for functional description.<br>See section 2.3.1 for external circuit design-in.                                                                                                        |

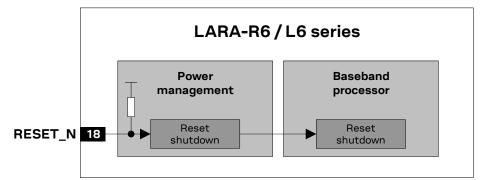

|          | RESET_N  | 18                                                                    | I   | External reset input                           | Internal pull-up to internal voltage domain.<br>Test-Point for diagnostic access is recommended.<br>See section 1.6.3 for functional description.<br>See section 2.3.2 for external circuit design-in.                                                                                                        |

| Antenna  | ANT1     | 56                                                                    | I/O | RF input/output for<br>main Tx/Rx antenna      | 50 Ω nominal characteristic impedance.<br>Antenna circuit affects the RF performance and<br>compliance of the device integrating the module with<br>applicable required certification schemes.<br>See section 1.7 for description and requirements.<br>See section 2.4 for external circuit design-in.        |

|          | ANT2     | 62                                                                    | I   | RF input for Rx<br>secondary antenna           | $50 \Omega$ nominal characteristic impedance.<br>Antenna circuit affects the RF performance and<br>compliance of the device integrating the module with<br>applicable required certification schemes.<br>See section 1.7 for description and requirements.<br>See section 2.4 for external circuit design-in. |

|          | ANT_DET  | 59                                                                    | I   | Input for antenna<br>detection                 | ADC for antenna presence detection function.<br>See section 1.7.2 for functional description.<br>See section 2.4.2 for external circuit design-in.                                                                                                                                                            |

| SIM      | VSIM     | 41                                                                    | 0   | SIM supply output                              | VSIM = 1.8 V / 3 V output as per the connected SIM type.<br>See section 1.8 for functional description.<br>See section 2.5 for external circuit design-in.                                                                                                                                                    |

|          | SIM_IO   | 39                                                                    | I/O | SIM data                                       | Data input/output for external 1.8 V/3 V SIM<br>Internal 4.7 k $\Omega$ pull-up to VSIM.<br>See section 1.8 for functional description.<br>See section 2.5 for external circuit design-in.                                                                                                                    |

|          | SIM_CLK  | 38                                                                    | 0   | SIM clock                                      | Clock output for external 1.8 V/3 V SIM<br>See section 1.8 for functional description.<br>See section 2.5 for external circuit design-in.                                                                                                                                                                     |

|          | SIM_RST  | 40                                                                    | 0   | SIM reset                                      | Reset output for external 1.8 V / 3 V SIM<br>See section 1.8 for functional description.<br>See section 2.5 for external circuit design-in.                                                                                                                                                                   |

| Function             | Pin name | Pin no. | I/O | Description                        | Remarks                                                                                                                                                                                                                                                                                                                                            |

|----------------------|----------|---------|-----|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

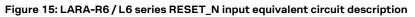

| UART                 | RXD      | 13      | 0   | UART data output                   | 1.8 V output, UART Circuit 104 (RXD) per ITU-T V.24,<br>supporting AT and data, FOAT, Multiplexer.<br>Test-Point and series 0 $\Omega$ for diagnostic to be considered.<br>See section 1.9.1.1 for functional description.<br>See section 2.6.1 for external circuit design-in.                                                                    |

|                      | TXD      | 12      | I   | UART data input                    | 1.8 V input, UART Circuit 103 (TXD) per ITU-T V.24,<br>supporting AT and data, FOAT, Multiplexer.<br>Internal active pull-up to V_INT.<br>Test-Point and series 0 $\Omega$ for diagnostic to be considered.<br>See section 1.9.1.1 for functional description.<br>See section 2.6.1 for external circuit design-in.                                |

|                      | CTS      | 11      | 0   | UART clear to send output          | 1.8 V output, UART Circuit 106 (CTS) per ITU-T V.24.<br>See section 1.9.1.1 for functional description.<br>See section 2.6.1 for external circuit design-in.                                                                                                                                                                                       |

|                      | RTS      | 10      | I   | UART ready to send input           | <ul><li>1.8 V input, UART Circuit 105 (RTS) per ITU-T V.24.</li><li>Internal active pull-up to V_INT.</li><li>See section 1.9.1.1 for functional description.</li><li>See section 2.6.1 for external circuit design-in.</li></ul>                                                                                                                  |

|                      | DSR      | 6       | 0   | UART data set ready<br>output      | <ul><li>1.8 V output, UART Circuit 107 (DSR) per ITU-T V.24.</li><li>Alternatively configurable as AUX UART RTS input.</li><li>See section 1.9.1.1 for functional description.</li><li>See section 2.6.1 for external circuit design-in.</li></ul>                                                                                                 |

|                      | RI       | 7       | 0   | UART ring indicator<br>output      | <ul><li>1.8 V output, UART Circuit 125 (RI) per ITU-T V.24.</li><li>Alternatively configurable as AUX UART CTS output.</li><li>See section 1.9.1.1 for functional description.</li><li>See section 2.6.1 for external circuit design-in.</li></ul>                                                                                                 |

|                      | DTR      | 9       | I   | UART data terminal ready input     | <ul> <li>1.8 V input, UART Circuit 108/2 (DTR) per ITU-T V.24.</li> <li>Internal active pull-up to V_INT.</li> <li>Alternatively configurable as AUX UART data input.</li> <li>See section 1.9.1.1 for functional description.</li> <li>See section 2.6.1 for external circuit design-in.</li> </ul>                                               |

|                      | DCD      | 8       | 0   | UART data carrier<br>detect output | 1.8 V input, UART Circuit 109 (DCD) per ITU-T V.24.<br>Alternatively configurable as AUX UART data output.<br>See section 1.9.1.1 for functional description.<br>See section 2.6.1 for external circuit design-in.                                                                                                                                 |

| AUX UAR <sup>-</sup> | I DCD    | 8       | 0   | AUX UART data<br>output            | 1.8 V output, AUX UART Circuit 104 (RXD) per ITU-T V.24,<br>supporting AT and data, FOAT.<br>The second auxiliary UART interface is disabled by default,<br>and it can be enabled by +USIO AT command.<br>See section 1.9.1.2 for functional description.<br>See section 2.6.1 for external circuit design-in.                                     |

|                      | DTR      | 9       | I   | AUX UART data<br>input             | 1.8 V input, AUX UART Circuit 103 (TXD) per ITU-T V.24,<br>supporting AT and data, FOAT.<br>Internal active pull-up to V_INT.<br>The second auxiliary UART interface is disabled by default,<br>and it can be enabled by +USIO AT command.<br>See section 1.9.1.2 for functional description.<br>See section 2.6.1 for external circuit design-in. |

|                      | RI       | 7       | 0   | AUX UART clear to send output      | 1.8 V output, AUX UART Circuit 106 (CTS) per ITU-T V.24.<br>See section 1.9.1.2 for functional description.<br>See section 2.6.1 for external circuit design-in.                                                                                                                                                                                   |

|                      | DSR      | 6       | I   | AUX UART ready to send input       | 1.8 V input, AUX UART Circuit 105 (RTS) per ITU-T V.24.<br>Internal active pull-up to V_INT.<br>See section 1.9.1.2 for functional description.<br>See section 2.6.1 for external circuit design-in.                                                                                                                                               |

| Function           | Pin name             | Pin no. | I/O | Description        | Remarks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|--------------------|----------------------|---------|-----|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| USB                | VUSB_DET             | 17      | I   | USB detect input   | VBUS (5 V typ) must be connected to this pin during the<br>switch-on boot sequence of the module to enable the USB<br>interface, supporting AT / data communication, FOAT,<br>GNSS tunneling, FW update by u-blox tool, diagnostic.<br>Test-Point for diagnostic / FW update highly recommended<br>See section 1.9.2 for functional description.<br>See section 2.6.2 for external circuit design-in.                                                                                                                                                                            |

|                    | USB_D-               | 28      | I/O | USB Data Line D-   | USB interface supporting AT / data communication, FOAT,<br>GNSS tunneling, FW update by u-blox tool, diagnostic.<br>90 $\Omega$ nominal differential impedance (ZO)<br>30 $\Omega$ nominal common mode impedance (ZCM)<br>Pull-up or pull-down resistors and external series resistors<br>as required by the USB 2.0 specifications [8] are part of the<br>USB pin driver and need not be provided externally.<br>Test-Point for diagnostic / FW update highly recommended<br>See section 1.9.2 for functional description.<br>See section 2.6.2 for external circuit design-in. |

|                    | USB_D+               | 29      | I/O | USB Data Line D+   | USB interface supporting AT / data communication, FOAT,<br>GNSS tunneling, FW update by u-blox tool, diagnostic.<br>$90 \Omega$ nominal differential impedance (ZO)<br>$30 \Omega$ nominal common mode impedance (ZCM)<br>Pull-up or pull-down resistors and external series resistors<br>as required by the USB 2.0 specifications [8] are part of the<br>USB pin driver and need not be provided externally.<br>Test-Point for diagnostic / FW update highly recommended<br>See section 1.9.2 for functional description.<br>See section 2.6.2 for external circuit design-in. |

| I2C                | SCL                  | 27      | Ο   | I2C bus clock line | $\begin{array}{l} 1.8 \mbox{ V open drain, for communication with external u-blox} \\ GNSS chips / modules, and other I2C devices. \\ Internal 2.2 \mbox{ k}\Omega \mbox{ pull-up resistor: no external pull-up required.} \\ See section 1.9.3 \mbox{ for functional description.} \\ See section 2.6.3 \mbox{ for external circuit design-in.} \end{array}$                                                                                                                                                                                                                    |

|                    | SDA                  | 26      | I/O | I2C bus data line  | $\begin{array}{l} 1.8 \mbox{ V open drain, for communication with external u-blox} \\ GNSS chips / modules, and other I2C devices. \\ Internal 2.2 \mbox{ k}\Omega \mbox{ pull-up resistor: no external pull-up required.} \\ See section 1.9.3 \mbox{ for functional description.} \\ See section 2.6.3 \mbox{ for external circuit design-in.} \end{array}$                                                                                                                                                                                                                    |

| Audio <sup>7</sup> | I2S_TXD <sup>8</sup> | 35      | 0   | I2S transmit data  | Digital audio data output.<br>Alternatively configurable as GPIO.<br>See sections 1.10 and 1.12 for functional description.<br>See sections 2.7 and 2.8 for external circuit design-in.                                                                                                                                                                                                                                                                                                                                                                                          |

|                    | I2S_RXD <sup>8</sup> | 37      | I   | I2S receive data   | Digital audio data input.<br>Alternatively configurable as GPIO.<br>See sections 1.10 and 1.12 for functional description.<br>See sections 2.7 and 2.8 for external circuit design-in.                                                                                                                                                                                                                                                                                                                                                                                           |

|                    | I2S_CLK <sup>8</sup> | 36      | 0   | I2S bit clock      | Digital audio bit clock.<br>Alternatively configurable as GPIO.<br>See sections 1.10 and 1.12 for functional description.<br>See sections 2.7 and 2.8 for external circuit design-in.                                                                                                                                                                                                                                                                                                                                                                                            |

|                    | I2S_WA <sup>8</sup>  | 34      | 0   | I2S word alignment | Digital audio word alignment synchronization signal.<br>Alternatively configurable as GPIO.<br>See sections 1.10 and 1.12 for functional description.<br>See sections 2.7 and 2.8 for external circuit design-in.                                                                                                                                                                                                                                                                                                                                                                |

<sup>&</sup>lt;sup>7</sup> LARA-R6001D, LARA-R6401D, LARA-R6801D, LARA-L6004D and LARA-L6804D data-only modules do not support voice / audio functionality.

<sup>&</sup>lt;sup>8</sup> I2S is not supported by data-only modules: I2S pins are by default set as Pin disabled.

| Function                        | Pin name             | Pin no.          | I/O | Description       | Remarks                                                                                                                                                                                                                                                 |

|---------------------------------|----------------------|------------------|-----|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Clock<br>output <sup>9</sup>    | GPIO6                | 19               | 0   | Clock output      | 1.8 V configurable clock output.<br>See section 1.11 for functional description.<br>See section 2.7 for external circuit design-in.                                                                                                                     |

| GPIO                            | GPIO1                | 16               | I/O | GPIO              | <ul> <li>1.8 V GPIO with alternatively configurable functions.</li> <li>See section 1.12 for functional description.</li> <li>See section 2.8 for external circuit design-in.</li> </ul>                                                                |

|                                 | GPIO2                | 23               | I/O | GPIO              | <ul> <li>1.8 V GPIO with alternatively configurable functions.</li> <li>See section 1.12 for functional description.</li> <li>See section 2.8 for external circuit design-in.</li> </ul>                                                                |

|                                 | GPIO3                | 24               | I/O | GPIO              | <ul><li>1.8 V GPIO with alternatively configurable functions.</li><li>See section 1.12 for functional description.</li><li>See section 2.8 for external circuit design-in.</li></ul>                                                                    |

|                                 | GPIO4                | 25               | I/O | GPIO              | <ul> <li>1.8 V GPIO with alternatively configurable functions.</li> <li>See section 1.12 for functional description.</li> <li>See section 2.8 for external circuit design-in.</li> </ul>                                                                |

|                                 | GPIO5                | 42               | I/O | GPIO              | <ul><li>1.8 V GPIO with alternatively configurable functions.</li><li>See section 1.12 for functional description.</li><li>See section 2.8 for external circuit design-in.</li></ul>                                                                    |

|                                 | I2S_TXD <sup>8</sup> | 35               | I/O | GPIO              | <ul><li>1.8 V GPIO with alternatively configurable functions.</li><li>See section 1.12 for functional description.</li><li>See section 2.8 for external circuit design-in.</li></ul>                                                                    |

|                                 | I2S_RXD <sup>8</sup> | 37               | I/O | GPIO              | <ul><li>1.8 V GPIO with alternatively configurable functions.</li><li>See section 1.12 for functional description.</li><li>See section 2.8 for external circuit design-in.</li></ul>                                                                    |

|                                 | I2S_CLK <sup>8</sup> | 36               | I/O | GPIO              | <ul><li>1.8 V GPIO with alternatively configurable functions.</li><li>See section 1.12 for functional description.</li><li>See section 2.8 for external circuit design-in.</li></ul>                                                                    |

|                                 | I2S_WA <sup>8</sup>  | 34               | I/O | GPIO              | <ul><li>1.8 V GPIO with alternatively configurable functions.</li><li>See section 1.12 for functional description.</li><li>See section 2.8 for external circuit design-in.</li></ul>                                                                    |

| Antenna<br>tuning <sup>10</sup> | RFCTRL1              | 97               | 0   | RF control output | <ul><li>1.8 V push-pull output to dynamically control external RF antenna tuning IC according to the cellular RF band in use.</li><li>See section 1.7.3 for functional description.</li><li>See section 2.4.3 for external circuit design-in.</li></ul> |

|                                 | RFCTRL2              | 98               | 0   | RF control output | <ul><li>1.8 V push-pull output to dynamically control external RF antenna tuning IC according to the cellular RF band in use.</li><li>See section 1.7.3 for functional description.</li><li>See section 2.4.3 for external circuit design-in.</li></ul> |

| Reserved                        | RSVD                 | 33               | N/A | RESERVED pin      | Pin with reserved use. Test-Point for diagnostic suggested.<br>See sections 1.13 and 2.9                                                                                                                                                                |

|                                 | RSVD                 | 2, 31            | N/A | RESERVED pin      | Pin reserved for future use. Internally not connected.<br>See sections 1.13 and 2.9                                                                                                                                                                     |

|                                 | RSVD                 | 44-49,<br>99,100 | N/A | RESERVED pin      | Pin reserved for future use. Leave unconnected.<br>See sections 1.13 and 2.9                                                                                                                                                                            |

|                                 | RSVD                 | 97-98            | N/A | RESERVED pin      | LARA-R6001-00B, LARA-R6001D-00B, LARA-R6801-00B,<br>LARA-L6004-00B, and LARA-L6004D-00B only.<br>Pin reserved for future use. See sections 1.13 and 2.9                                                                                                 |

Table 3: LARA-R6 / L6 series modules pin definition, grouped by function

<sup>&</sup>lt;sup>9</sup> LARA-R6001D, LARA-R6401D, LARA-R6801D, LARA-L6004D and LARA-L6804D data-only modules do not support GPIO6 clock output.

<sup>&</sup>lt;sup>10</sup> LARA-R6001-00B, LARA-R6001D-00B, LARA-R6801-00B, LARA-L6004-00B and LARA-L6004D-00B product versions do not support antenna tuning interface: related pins are reserved for future use (RSVD).

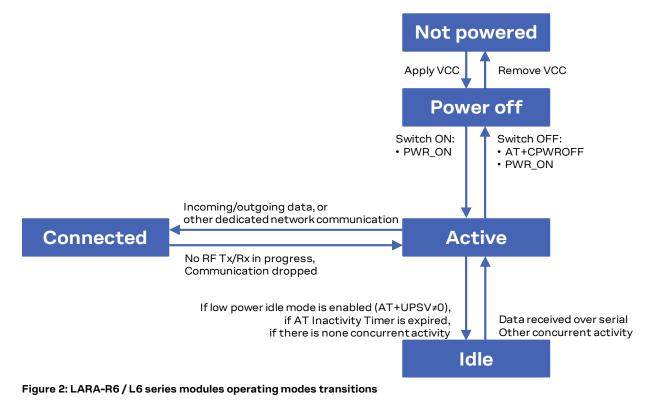

## 1.4 Operating modes

| General status   | Operating mode   | Definition                                                                       |  |

|------------------|------------------|----------------------------------------------------------------------------------|--|

| Power-down       | Not-powered mode | VCC supply not present or below operating range: module is switched off.         |  |

|                  | Power-off mode   | VCC supply within operating range and module is switched off.                    |  |

| Normal Operation | Idle mode        | Module processor runs at the minimum frequency to save power consumption.        |  |

|                  | Active mode      | Module processor runs at normal operating frequency to enable related functions. |  |

|                  | Connected mode   | RF Tx/Rx enabled with processor running at related operating frequency.          |  |

LARA-R6 / L6 series modules have several operating modes, which are defined in Table 4.

Table 4: Module operating modes definition

The initial operating mode of LARA-R6 / L6 series modules has the **VCC** supply not present or below the operating range: the modules are switched off in not-powered mode.

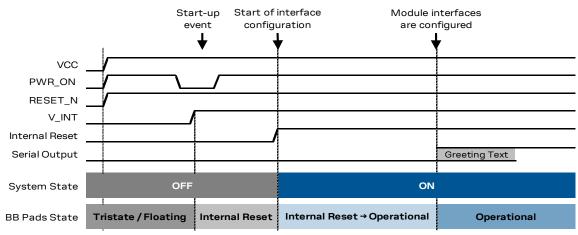

Once a valid **VCC** supply is applied to the LARA-R6 / L6 series modules, they remain switched off in the power-off mode. Then the proper toggling of the **PWR\_ON** input line is necessary to trigger the switch-on routine of the modules that subsequently enter the active mode.

LARA-R6/L6 series modules are ready to operate when in active mode. The available communication interfaces are ready and the module can accept and respond to AT commands, entering connected mode upon cellular RF signal reception/transmission.

LARA-R6/L6 series modules switch from active mode to the low power idle mode whenever possible, if the low power configuration is enabled by the dedicated +UPSV AT command. The low power idle mode can last for different time periods according to the specific +UPSV AT command setting, according to the DRX/eDRX setting, and according to the concurrent activities executed.

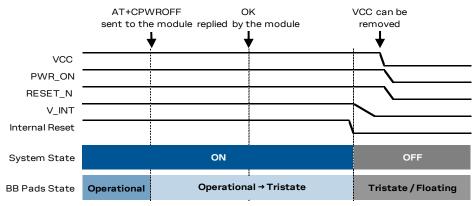

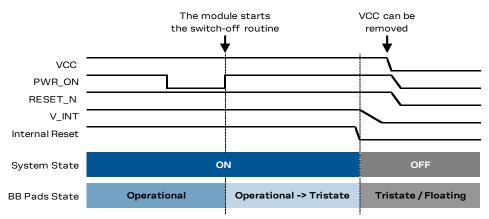

LARA-R6 / L6 series modules can be gracefully switched off by the dedicated +CPWROFF AT command, or by proper toggling of the **PWR\_ON** input line.

Figure 2 summarizes the transition between the different operating modes.

# 1.5 Supply interfaces

## 1.5.1 Module supply input (VCC)

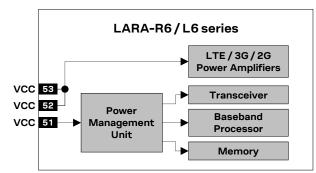

The modules must be supplied via the three VCC pins that represent the module power supply input.

The **VCC** pins are internally connected to the RF power amplifier and to the integrated Power Management Unit: all supply voltages needed by the module are generated from the **VCC** supply by integrated voltage regulators, including the **V\_INT** supply for generic digital interfaces (as the UARTs, I2C, I2S, GPIOs) and the **VSIM** supply for the SIM interface.

During operation, the current drawn by the LARA-R6 / L6 series modules through the **VCC** pins can vary by several orders of magnitude. This ranges from the pulse of current consumption during GSM transmitting bursts at maximum power level in connected mode (as described in section 1.5.1.4) to the low current consumption during the low power idle mode (as described in section 1.5.1.5).

LARA-R6 / L6 series modules provide separate supply inputs over the three VCC pins:

- VCC pins #52 and #53 represent the supply input for the internal RF power amplifier, demanding most of the total current drawn of the module when RF transmission is enabled during a voice/data call

- VCC pin #51 represents the supply input for the internal baseband Power Management Unit and the internal transceiver, demanding minor part of the total current drawn of the module when RF transmission is enabled during a voice/data call

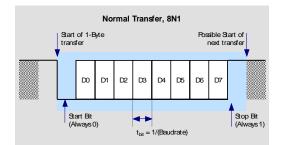

Figure 3 provides a basic block diagram of LARA-R6 / L6 series modules internal VCC supply routing.

Figure 3: LARA-R6 / L6 series modules internal VCC supply routing simplified block diagram

#### 1.5.1.1 VCC supply requirements

Table 5 summarizes the requirements for the VCC module supply. See section 2.2.1 for all the suggestions to properly design a VCC supply circuit compliant to the requirements listed in Table 5.

▲ VCC supply circuit affects the RF compliance of the device integrating LARA-R6 / L6 series modules with applicable required certification schemes as well as antenna circuit design. RF performance is optimized by fulfilling the requirements for VCC supply summarized in Table 5.

| Operating within 3GPP / ETSI specifications: RF<br>performance is optimized when <b>VCC</b> PA voltage is<br>inside the normal operating range limits.<br>e: Operating with possible slight deviation in RF                                                                                                                                                                                                                                                             |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| e. Operating with possible slight deviation in RF                                                                                                                                                                                                                                                                                                                                                                                                                       |

| <ul> <li>Performance outside normal operating range.</li> <li>VCC voltage must be above the extended operating range minimum limit to switch-on the module and to avoid possible switch-off of the module.</li> <li>Operation above VCC extended operating range is not recommended and may affect device reliability.</li> </ul>                                                                                                                                       |

| ghest<br>alue in<br>in theThe highest averaged VCC current consumption can<br>be greater than the specified value according to the<br>actual antenna mismatching, temperature and VCC<br>voltage.For a safe design margin, use a VCC supply source<br>that can deliver double the typical average VCC<br>current consumption at maximum Tx power, normal<br>ambient temperature and normal voltage condition<br>shown in the LARA-R6 / L6 series data sheet [1][2].<br> |

| <ul> <li>CCC The specified highest peak of VCC current</li> <li>ted mode consumption occurs during GSM single transmit slot</li> <li>L6 series in 850/900 MHz connected mode, in case of a mismatched antenna.</li> <li>See 1.5.1.4 for 2G connected mode current profiles.</li> </ul>                                                                                                                                                                                  |

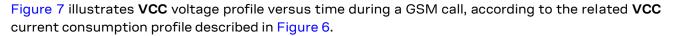

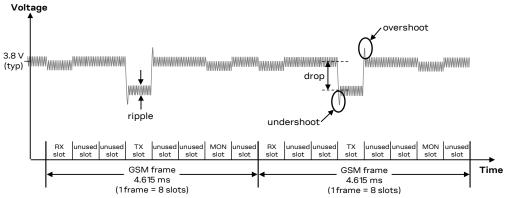

| <b>VCC</b> voltage drop directly affects the RF compliance<br>with applicable certification schemes.<br>Figure 7 describes <b>VCC</b> voltage drop during Tx slots.                                                                                                                                                                                                                                                                                                     |

| d VCC voltage ripple directly affects the RF<br>compliance with applicable certification schemes.<br>Figure 7 describes VCC voltage ripple during Tx slots.                                                                                                                                                                                                                                                                                                             |

| VCC under/over-shoot directly affects the RF compliance with applicable certification schemes.<br>Figure 7 describes VCC voltage under/over-shoot.                                                                                                                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

Table 5: Summary of VCC supply requirements

#### 1.5.1.2 VCC consumption in LTE connected mode

During an LTE connection, the module may transmit and receive continuously due to the frequency division duplex (FDD) mode of operation or it may transmit and receive alternatively due to the time division duplex (TDD) mode of operation available with LTE radio access technology.

The current consumption depends on output RF power, which is always regulated by the network (the current base station) sending power control commands to the module. These power control commands are logically divided into a slot of 0.5 ms (time length of one Resource Block), thus the rate of power change can reach a maximum rate of 2 kHz.

In the worst case scenario, corresponding to a continuous transmission and reception at maximum output power (approximately 0.25 W), the average current drawn by the module at the VCC pins is considerable (see the "Current consumption" section in LARA-R6 / L6 series data sheet [1][2]). At the lowest output RF power (approximately 0.1  $\mu$ W), the current drawn by the internal power amplifier is strongly reduced and the total current drawn by the module at the VCC pins is due to baseband processing and transceiver activity.

The maximum peak of current consumption in LTE is similar to that in 3G radio access technology, because in both cases the maximum output RF power is roughly 0.25 W. In the LTE connected mode, as in the 3G connected mode, there are no high current peaks like the 2G connection mode, which uses the Time Division Multiple Access (TDMA) mode of operation, because the maximum output RF power in the 2G low bands (850 MHz or 900 MHz) is roughly 2.0 W.

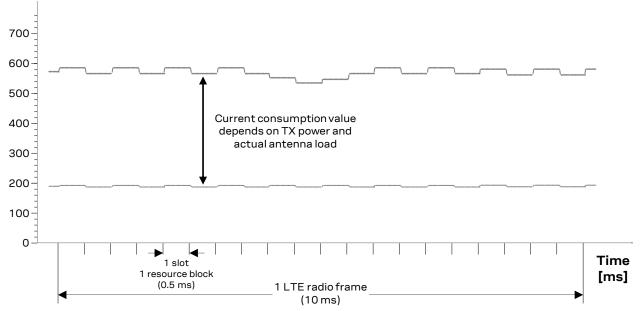

Figure 4 shows an example of the module current consumption profile versus time in the LTE FDD connected mode. Detailed current consumption values can be found in LARA-R6 / L6 series data sheet [1][2].

Current [mA]

Figure 4: VCC current consumption profile versus time during LTE connection (TX and RX continuously enabled)

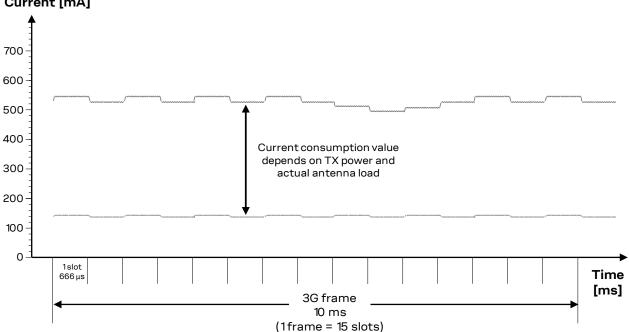

#### 1.5.1.3 VCC consumption in 3G connected mode

During a 3G connection, the module can transmit and receive continuously due to the frequency division duplex (FDD) mode of operation with the wideband code division multiple access (WCDMA).

The current consumption depends on output RF power, which is always regulated by the network (the current base station) sending power control commands to the module. These power control commands are logically divided into a slot of 666 µs, so the rate of power change can reach a maximum rate of 1.5 kHz.

There are no high current peaks as in the 2G connection, since transmission and reception are continuously enabled due to FDD WCDMA implemented in the 3G that differs from the TDMA implemented in the 2G case.

In the worst case scenario, corresponding to a continuous transmission and reception at maximum output power (approximately 0.25 W), the average current drawn by the module at the VCC pins is considerable (see the "Current consumption" section in LARA-R6/L6 series data sheet [1] [2]). At the lowest output RF power (approximately 0.01  $\mu$ W), the current drawn by the internal power amplifier is strongly reduced. The total current drawn by the module at the VCC pins is due to baseband processing and transceiver activity.

Figure 5 shows an example of the current consumption profile of the module in 3G WCDMA/HSPA continuous transmission mode.

#### Current [mA]

Figure 5: VCC current consumption profile versus time during a 3G connection (TX and RX continuously enabled)

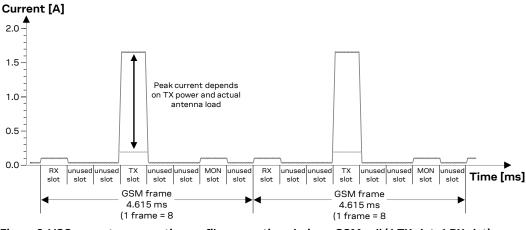

#### 1.5.1.4 VCC consumption in 2G connected mode

When a GSM call is established, the **VCC** consumption is determined by the current consumption profile typical of the GSM transmitting and receiving bursts.

The current consumption peak during a transmission slot is strictly dependent on the transmitted power, which is regulated by the network. The transmitted power in the transmit slot is also the more relevant factor for determining the average current consumption.

If the module is transmitting in 2G single-slot mode (as in GSM talk mode) in the 850 or 900 MHz bands, at the maximum RF power control level (approximately 2 W or 33 dBm in the Tx slot/burst), the current consumption can reach an high peak / pulse (see LARA-R6 / L6 series data sheet [1] [2]) for 576.9  $\mu$ s (width of the Tx slot/burst) with a periodicity of 4.615 ms (width of 1 frame = 8 slots/burst), so with a 1/8 duty cycle according to GSM TDMA (Time Division Multiple Access).

If the module is transmitting in 2G single-slot mode in the 1800 or 1900 MHz bands, the current consumption figures are quite less high than the one in the low bands, due to the 3GPP transmitter output power specifications.

During a GSM call, current consumption is not so significantly high in receiving or in monitor bursts and it is low in the bursts unused to transmit / receive.

Figure 6 shows an example of the module current consumption profile versus time in GSM talk mode.

Figure 7: Description of the VCC voltage profile versus time during a GSM call (1 TX slot, 1 RX slot)

#### 1.5.1.5 VCC consumption in low power idle mode

The power saving configuration is disabled by default, but it can be enabled using the appropriate AT command (see the AT commands manual [3], +UPSV AT command). When power saving is enabled, the module automatically enters low power idle mode whenever possible, reducing consumption.

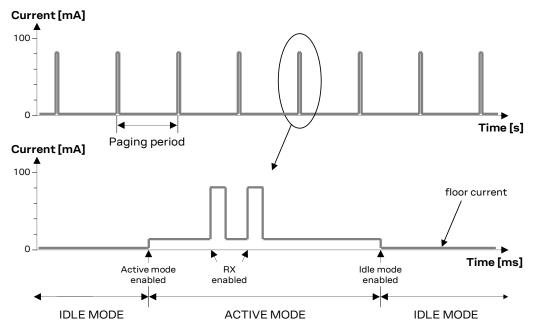

When the power saving configuration is enabled and the module is registered or attached to a network, the module automatically enters the low power idle mode whenever possible, but it must periodically monitor the paging channel of the current base station (paging block reception), in accordance to the 2G/3G/LTE system requirements, even if the connected mode is not enabled by the application. When the module monitors the paging channel, it wakes up to the active mode to enable the reception of the paging block. In between, the module switches to low power idle mode. This is known as discontinuous reception (DRX) or extended discontinuous reception (eDRX).

Figure 8 illustrates a typical example of the module current consumption profile when power saving is enabled. The module is registered with the network, automatically enters the low power idle mode and periodically wakes up to active mode to monitor the paging channel for the paging block reception. Detailed current consumption values can be found in the LARA-R6 / L6 series data sheet [1] [2]).

Figure 8: VCC current consumption profile with power saving enabled and module registered with the network: the module is in low-power idle mode and periodically wakes up to active mode to monitor the paging channel for paging block reception

#### 1.5.1.6 VCC consumption in active mode (low power idle mode disabled)

The active mode is the state where the module is switched on and ready to communicate with an external device by means of the application interfaces (as the USB or the UART serial interface). The module processor core is active, and the 19.2 MHz reference clock frequency is used.

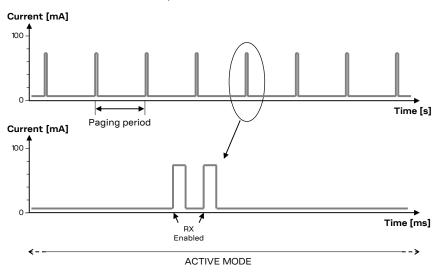

If the low power idle mode configuration is disabled, as it is by default (see the AT commands manual [3], +UPSV AT commands for details), the module remains in active mode. Otherwise, if the low power idle mode configuration is enabled, the module enters the low power idle mode whenever possible, reducing consumption.

Figure 9 illustrates a typical example of the module current consumption profile when power saving is disabled. In such case, the module is registered with the network and while active mode is maintained, the receiver is periodically activated to monitor the paging channel for paging block reception. Detailed current consumption values can be found in the LARA-R6/L6 series data sheet [1] [2].

Figure 9: VCC current consumption profile with power saving disabled and module registered with the network: active mode is always held and the receiver is periodically activated to monitor the paging channel for paging block reception

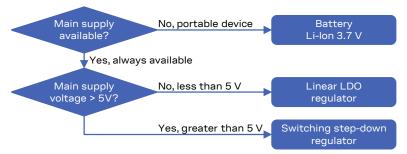

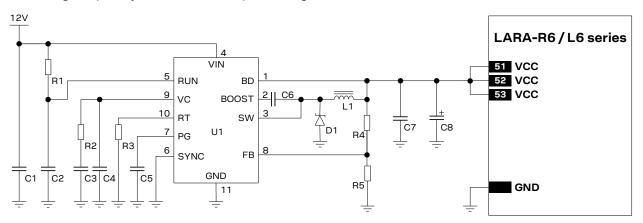

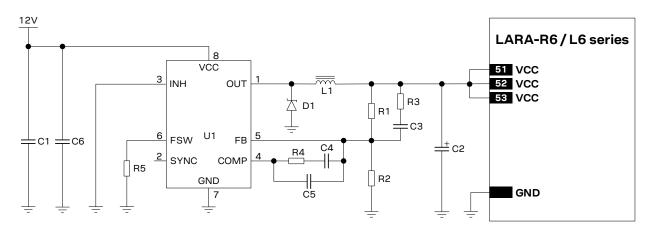

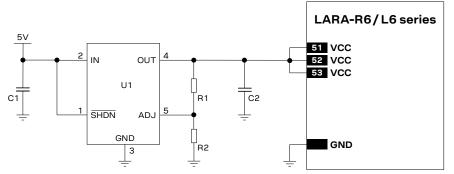

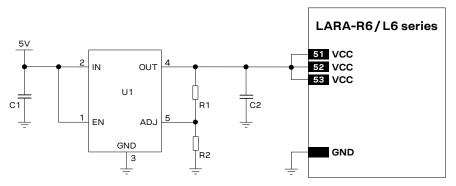

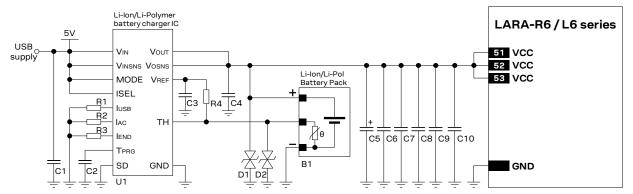

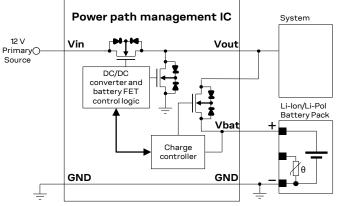

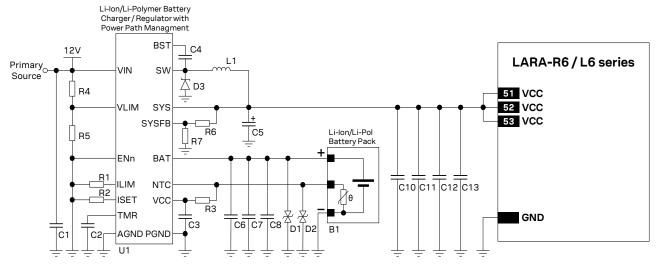

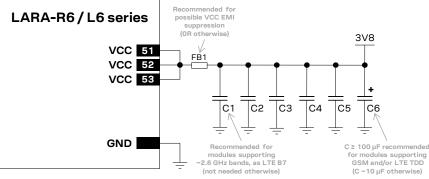

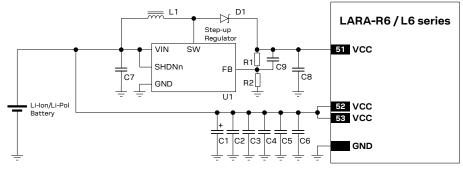

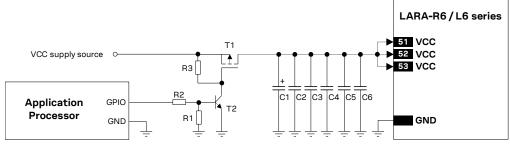

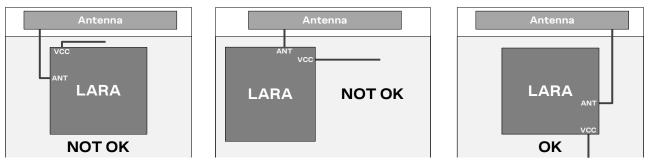

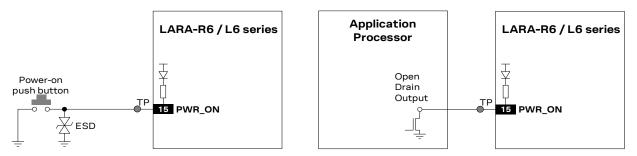

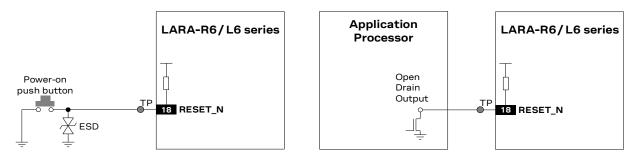

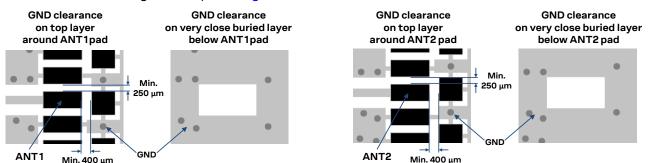

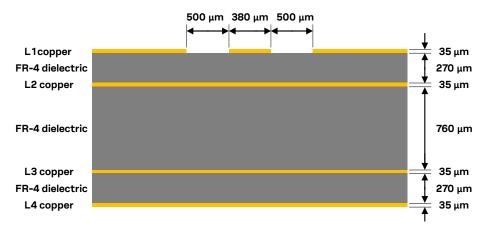

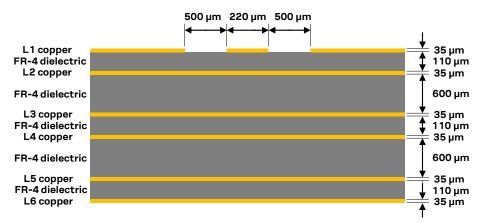

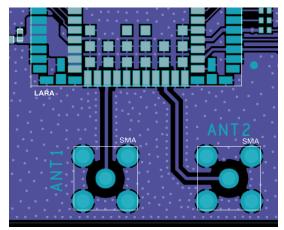

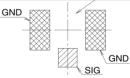

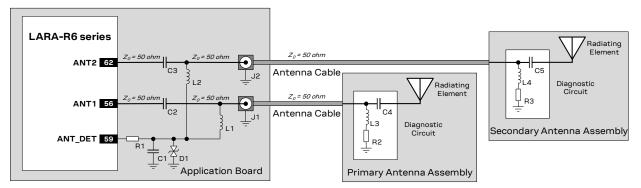

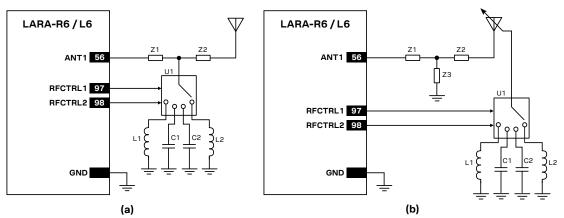

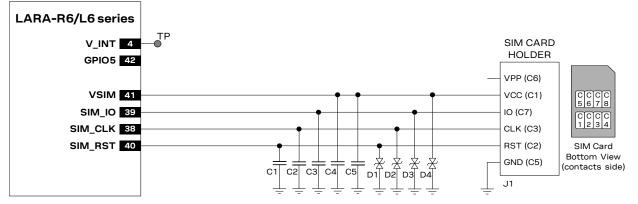

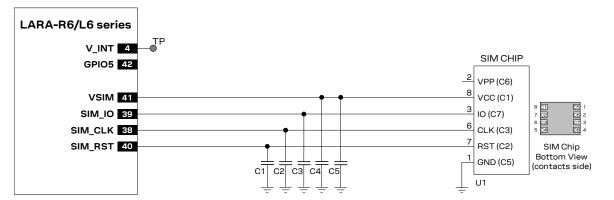

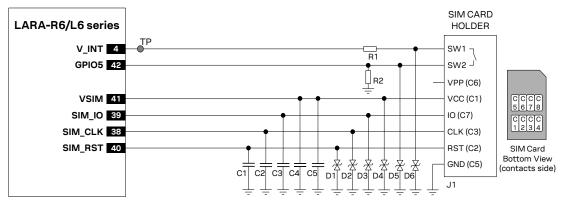

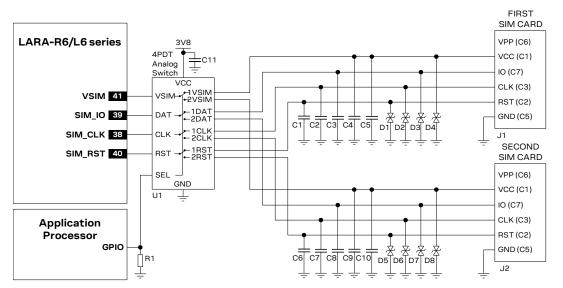

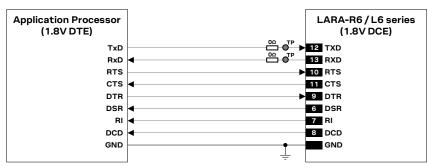

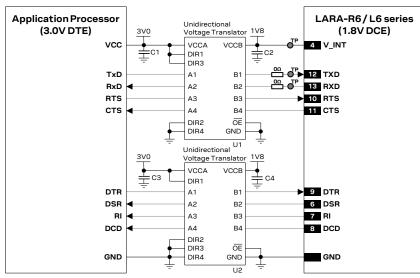

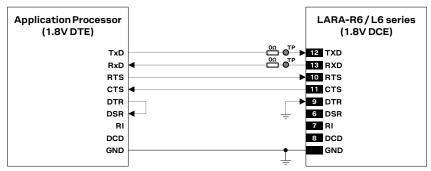

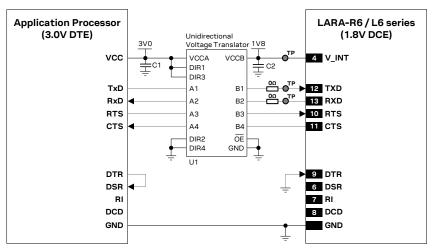

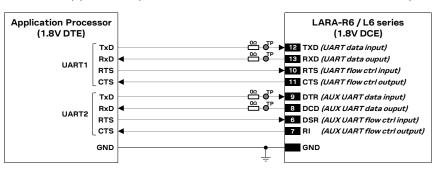

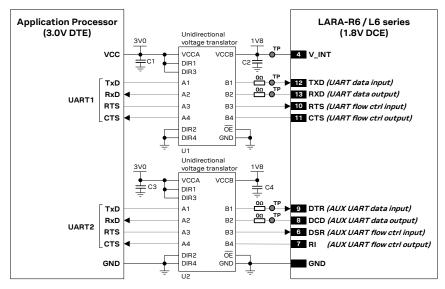

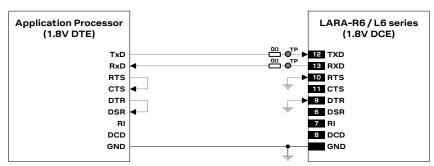

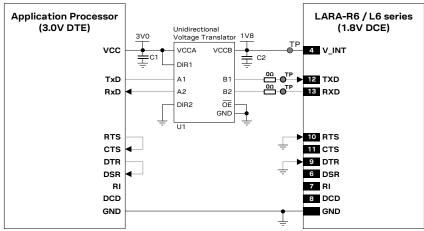

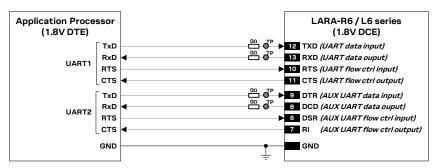

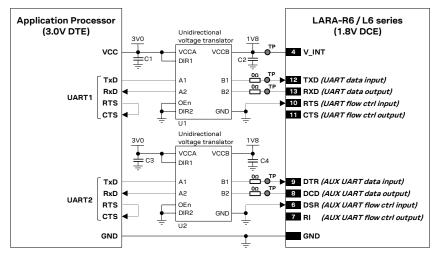

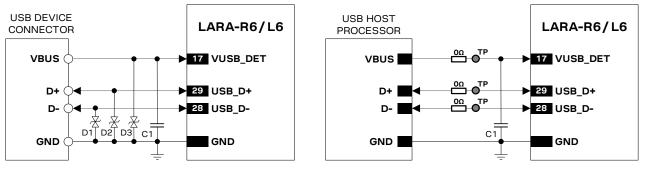

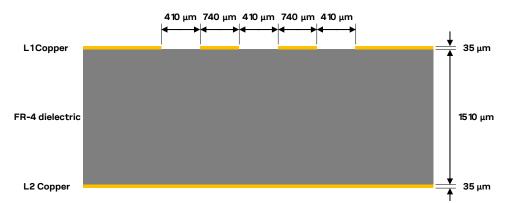

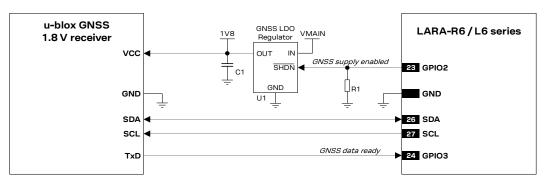

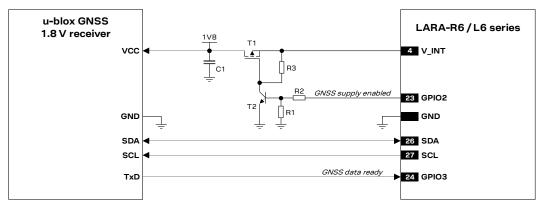

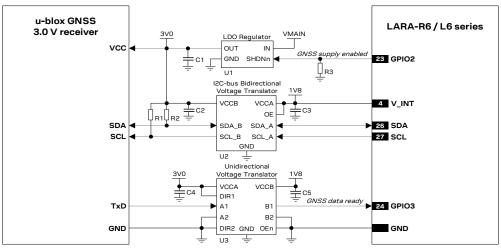

## 1.5.2 Generic digital interfaces supply output (V\_INT)