NAU7802 24-bit ADC

# nuvoTon

# NAU7802

# 24-Bit Dual-Channel ADC

# **For Bridge Sensors**

Date: January, 2012

**Revision 1.7**

- 1 -

Nuvoton Confidential

Revision 1.7

### Table of Contents

| 2         SYSTEM BLOCK DIAGRAM         4           3         FEATURES         4           4         APPLICATIONS         5           5         PIN CONFIGURATION         6           6         PIN DESCRIPTION         6           7         TL ONFIGURATION         6           7         TL ONFIGURATION         6           7         TL ONFIGURATION         6           7         TL ONFIGURATION         6           7         TL Absolute Maximum Ratings         7           7.1         Absolute Maximum Ratings         7           7.2         DC ELECTRICAL CHARACTERISTICS         7           7.3         RC OSC AND AC CHARACTERISTICS         7           7.4         TEMPERATURE SENSOR         9           7.5         Typical Characteristic.         10           7.5.1         NAU7802 Linearity - (Error % vs. Input Voltage)         10           7.5.2         Noise Performance - NAU7802         11           7.6         DIGITAL SERIAL INTERFACE TIMINC         12           8         FUNCTIONAL DESCRIPTION         13           8.1         Analog input (VINP, VINN, VIN2P)         13           8.2         Power supply         13<                                                                               | 1 | GENE | ERAL DESCRIPTION                       | 4  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|------|----------------------------------------|----|

| 4         APPLICATIONS         5           5         PIN CONFIGURATION         6           6         PIN DESCRIPTION         6           7         ELECTRICAL CHARACTERISTICS         7           7.1         Absolute Maximum Ratings         7           7.2         DC ELECTRICAL CHARACTERISTICS         7           7.3         R COSC AND AC CHARACTERISTICS         7           7.4         TEMPERATURE SENSOR         9           7.5         Typical Characteristic         10           7.5.1         NAU7802 Linearity – (Error % vs. Input Voltage)         10           7.5.2         Noise Performance – NAU7802         11           7.6         DIGITAL SERIAL INTERFACE TIMING         12           7.6         DIGITAL SERIAL INTERFACE TIMING         12           8         FUNCTIONAL DESCRIPTION         13           8.1         Analog input (VINP, VINN, VIN2N, VIN2P)         13           8.2         Power supply         13           8.3         2-Wire Frotocol Convention         14           8.3.2         2-Wire Write Operation         16           8.3.3         2-Wire Streaming Data Mode         18           8.5.1         Enabling the Strearming I2C Mode RW Protocol 1                                 | 2 | SYST | EM BLOCK DIAGRAM                       | 4  |

| 4         APPLICATIONS         5           5         PIN CONFIGURATION         6           6         PIN DESCRIPTION         6           7         ELECTRICAL CHARACTERISTICS         7           7.1         Absolute Maximum Ratings         7           7.2         DC ELECTRICAL CHARACTERISTICS         7           7.3         R COSC AND AC CHARACTERISTICS         7           7.4         TEMPERATURE SENSOR         9           7.5         Typical Characteristic         10           7.5.1         NAU7802 Linearity – (Error % vs. Input Voltage)         10           7.5.2         Noise Performance – NAU7802         11           7.6         DIGITAL SERIAL INTERFACE TIMING         12           7.6         DIGITAL SERIAL INTERFACE TIMING         12           8         FUNCTIONAL DESCRIPTION         13           8.1         Analog input (VINP, VINN, VIN2N, VIN2P)         13           8.2         Power supply         13           8.3         2-Wire Frotocol Convention         14           8.3.2         2-Wire Write Operation         16           8.3.3         2-Wire Streaming Data Mode         18           8.5.1         Enabling the Strearming I2C Mode RW Protocol 1                                 | 3 | FEAT | URES                                   | 4  |

| 5       PIN CONFIGURATION       6         6       PIN DESCRIPTION       6         7       ELECTRICAL CHARACTERISTICS       7         7.1       Absolute Maximum Ratings       7         7.2       DC ELECTRICAL CHARACTERISTICS       7         7.3       RC OSC AND AC CHARACTERISTICS       9         7.4       TEMPERATURE SENSOR       9         7.5       Typical Characteristic       10         7.5.1       NAU7802 Lineanty – (Error % vs. Input Voltage)       10         7.5.2       Noise Performance – NAU7802       11         7.5.3       ESD Performance – NAU7802       11         7.5.4       DIGITAL SERIAL INTERFACE TIMING       12         8       FUNCTIONAL DESCRIPTION       13         8.1       Analog input (VIN1P, VIN1N, VIN2N, VIN2P)       13         8.2       Power supply       13         8.3       2-Wire Protocol Convention       14         8.3.2       2-Wire Write Operation       16         8.3.3       2-Wire Write Operation       16         8.4.3       2-Wire Write OPeration       16         8.5.1       Enabling the Streaming 12C Mode       18         8.5.2       Streaming 12C Mode RW Protocol 1 <t< td=""><td>4</td><td></td><td></td><td></td></t<>                                       | 4 |      |                                        |    |

| 6       PIN DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 5 |      |                                        |    |

| 7       ELECTRICAL CHARACTERISTICS       7         7.1       Absolute Maximum Ratings       7         7.2       DC ELECTRICAL CHARACTERISTICS       7         7.3       RC OSC AND AC CHARACTERISTICS       9         7.4       TEMPERATURE SENSOR       9         7.5       Typical Characteristic       10         7.5.1       NAU7802 Linearity - (Erro % vs. Input Voltage)       10         7.5.2       Noise Performance - NAU7802       11         7.6       DIGITAL SERIAL INTERFACE TIMING       12         8       FUNCTIONAL DESCRIPTION       13         8.1       Analog input (VIN1P, VIN1N, VIN2N, VIN2P)       13         8.2       Power supply       13         8.3       2-Wire Virie Operation       16         8.3.3       2-Wire Write Operation       16         8.4.2       2-Wire Write Operation       16         8.5.1       Enabling the Streaming 12C Mode       18         8.5.2       Streaming 12C Mode RW Protocol 2       19         8.6 <t< td=""><td>-</td><td>-</td><td></td><td>-</td></t<>                            | - | -    |                                        | -  |

| 7.1       Absolute Maximum Ratings       7         7.2       DC ELECTRICAL CHARACTERISTICS       7         7.3       RC OSC AND AC CHARACTERISTICS       9         7.4       TEMPERATURE SENSOR       9         7.5       Typical Characteristic       10         7.5.1       NAU7802 Linearity – (Error % vs. Input Voltage)       10         7.5.2       Noise Performance – NAU7802       11         7.5.3       SED Performance – NAU7802       11         7.6       DIGITAL SERIAL INTERFACE TIMING       12         8       FUNCTIONAL DESCRIPTION       13         8.1       Analog input (VIN1P, VIN1N, VIN2N, VIN2P)       13         8.2       Power supply       13         8.3       2-Wire Orotocl Convention       14         8.3.1       2-Wire Write Operation       16         8.3.3       2-Wire Write Operation       16         8.5.1       Enabling the Streaming I2C Mode       18         8.5.2       Streaming I2C Mode RW Protocol 1       18         8.5.3       Streaming I2C Mode RW Protocol 1       18         8.5.4       Calibration Features       20         8.6.1       Internal Band-Gap Circuit       22         8.7       Intern                                                                              | - |      |                                        |    |

| 7.2       DC ELECTRICAL CHARACTERISTICS       7         7.3       RC OSC AND AC CHARACTERISTICS       9         7.4       TEMPERATURE SENSOR.       9         7.5       Typical Characteristic.       10         7.5.1       NAU7802 Linearity - (Error % vs. Input Voltage)       10         7.5.2       Noise Performance - NAU7802       11         7.6       DIGITAL SERIAL INTERFACE TIMING       12         8       FUNCTIONAL DESCRIPTION       13         8.1       Analog input (VIN1P, VIN1N, VIN2N, VIN2P)       13         8.2       Power supply       13         8.3.1       2-Wire Protocol Convention       14         8.3.2       2-Wire Vire Operation       16         8.3.3       2-Wire Single Read Operation       16         8.4.1       2-Wire Vire Operation       18         8.5.2       Streaming Data Mode       18         8.5.3       Streaming I2C Mode R/W Protocol 1       18         8.5.3       Streaming I2C Mode R/W Protocol 2       19         8.6       Device Calibration Features       20         8.6.1       Internal calibration.       21         8.6       Calibration Error       21         8.6       Calibration Err                                                                              | • |      |                                        |    |

| 7.3       RC OSC AND AC CHARACTERISTICS       9         7.4       TEMPERATURE SENSOR       9         7.5       Typical Characteristic       10         7.5.1       NAU7802 Linearity - (Error % vs. Input Voltage)       10         7.5.2       Noise Performance - NAU7802       11         7.6       DIGITAL SERIAL INTERFACE TIMING       12         8       FUNCTIONAL DESCRIPTION       13         8.1       Analog input (VIN1P, VIN1N, VIN2N, VIN2P)       13         8.2       Power supply       13         8.3       2-Wire-Serial Control and Data Bus (I <sup>2</sup> C Style Interface)       13         8.3.1       2-Wire Write Operation       16         8.3.2       2-Wire Write Operation       16         8.3.3       2-Wire Single Read Operation       16         8.5.1       Enabling the Streaming I2C Mode       18         8.5.2       Streaming I2C Mode R/W Protocol 1       18         8.5.3       Streaming I2C Mode R/W Protocol 2       19         8.6       Device Calibration Features       20         8.6.1       Internal or External calibration       20         8.6.2       Calibration Error       21         8.6.3       Calibration Error       21 <tr< td=""><td></td><td></td><td></td><td></td></tr<> |   |      |                                        |    |

| 7.4       TEMPERATURE SENSOR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   |      |                                        |    |

| 7.5       Typical Characteristic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |      |                                        |    |

| 7.5.1       NAU7802 Linearity – (Error % vs. Input Voltage)       10         7.5.2       Noise Performance – NAU7802       11         7.5.3       ESD Performance – NAU7802       11         7.6       DIGITAL SERIAL INTERFACE TIMING       12         8       FUNCTIONAL DESCRIPTION       13         8.1       Analog input (VIN1P, VIN1N, VIN2N, VIN2P)       13         8.2       Power supply       13         8.3       2-Wire-Serial Control and Data Bus (I <sup>2</sup> C Style Interface)       13         8.3.1       2-Wire Protocol Convention       14         8.3.2       2-Wire Write Operation       16         8.3.3       2-Wire Write Operation       16         8.3.3       2-Wire Timing       17         8.5       NAU7802 Streaming Data Mode       18         8.5.1       Enabing the Streaming 12C Mode       18         8.5.2       Streaming 12C Mode R/W Protocol 1       18         8.5.3       Streaming 12C Mode R/W Protocol 2       19         8.6       Device Calibration Features       20         8.6.1       Internal or External calibration       20         8.6.2       Calibration Error       21         8.7       Internal Crystal Oscillator       22                                                |   |      |                                        |    |

| 7.5.2       Noise Performance – NAU7802                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   | 7.0  |                                        |    |

| 7.5.3       ESD Performance – NAU7802                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   |      |                                        |    |

| 7.6       DIGITAL SERIAL INTERFACE TIMING       .12         8       FUNCTIONAL DESCRIPTION       .13         8.1       Analog input (VIN1P, VIN1N, VIN2P)       .13         8.2       Power supply       .13         8.3       2-Wire-Serial Control and Data Bus (I <sup>2</sup> C Style Interface)       .13         8.3.1       2-Wire Fotocol Convention       .14         8.3.2       2-Wire Write Operation       .16         8.3.3       2-Wire Single Read Operation       .16         8.4       2-Wire Timing       .17         8.5       NAU7802 Streaming Data Mode       .18         8.5.1       Enabling the Streaming I2C Mode       .18         8.5.2       Streaming I2C Mode R/W Protocol 1       .18         8.5.3       Streaming I2C Mode R/W Protocol 2       .19         8.6       Device Calibration Features       .20         8.6.1       Internal or External calibration.       .20         8.6.2       Calibration Error       .21         8.7       Internal Band-Gap Circuit       .22         8.8       Reset and Power-down mode       .22         8.9       Temperature sensor       .23         8.10       Oscillator Features       .24         8.10.1<                                                          |   |      |                                        |    |

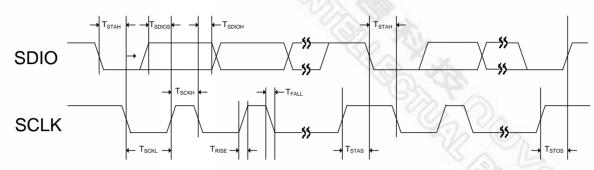

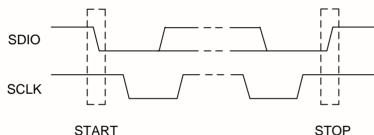

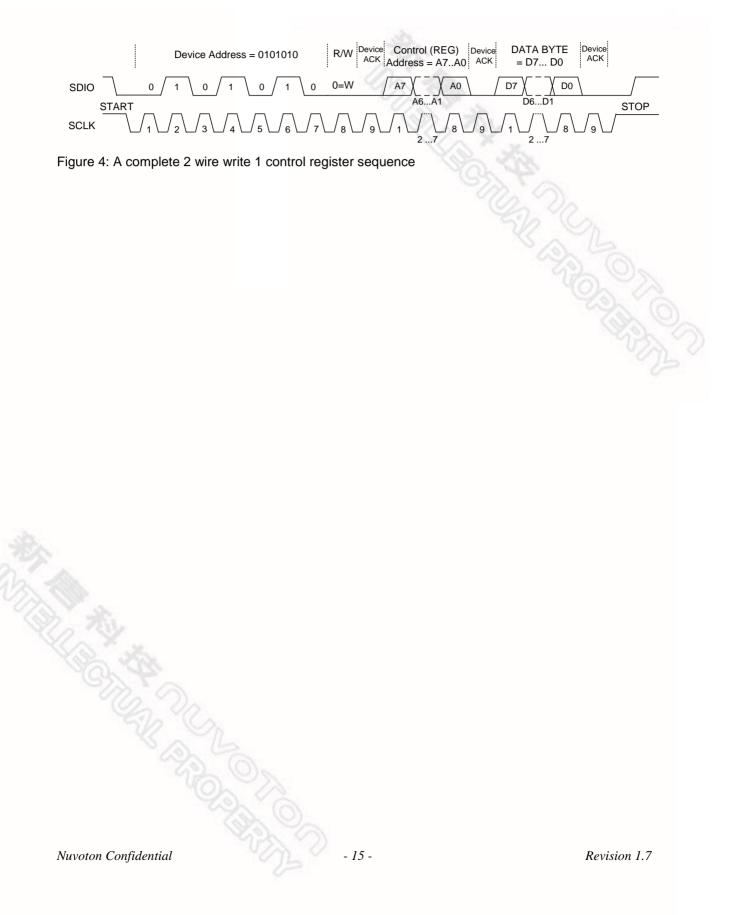

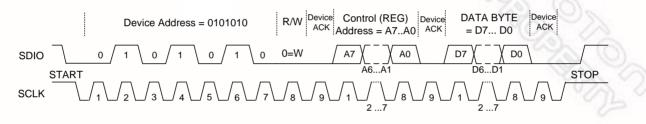

| 8       FUNCTIONAL DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |   | 7.6  |                                        |    |

| 8.1       Analog input (VIN1P, VIN1N, VIN2N, VIN2P)       13         8.2       Power supply       13         8.3       2-Wire-Serial Control and Data Bus (I <sup>2</sup> C Style Interface)       13         8.3.1       2-Wire Protocol Convention       14         8.3.2       2-Wire Write Operation       16         8.3.3       2-Wire Single Read Operation       16         8.4       2-Wire Timing       17         8.5       NAU7802 Streaming Data Mode       18         8.5.1       Enabling the Streaming I2C Mode       18         8.5.2       Streaming I2C Mode RW Protocol 1       18         8.5.3       Streaming I2C Mode RW Protocol 2       19         8.6       Device Calibration Features       20         8.6.1       Internal or External calibration       20         8.6.2       Calibration Error       21         8.6       Calibration Error       21         8.7       Internal Band-Gap Circuit       22         8.8       Reset and Power-down mode       22         8.9       Temperature sensor       23         8.10       Oscillator Features       24         8.10.1       External Clock Source       24         8.10.2       External C                                                                   | 8 |      |                                        |    |

| 8.2       Power supply       13         8.3       2-Wire-Serial Control and Data Bus (I <sup>2</sup> C Style Interface)       13         8.3.1       2-Wire Protocol Convention       14         8.3.2       2-Wire Write Operation       16         8.3.3       2-Wire Single Read Operation       16         8.4       2-Wire Timing.       17         8.5       NAU7802 Streaming Data Mode       18         8.5.1       Enabling the Streaming I2C Mode       18         8.5.2       Streaming I2C Mode R/W Protocol 1       18         8.5.3       Streaming I2C Mode R/W Protocol 2       19         8.6       Device Calibration Features       20         8.6.1       Internal or External calibration.       20         8.6.2       Calibration Limitations       21         8.6.3       Calibration Error       21         8.6.4       Calibration Error       21         8.7       Internal Band-Gap Circuit       22         8.8       Reset and Power-down mode       22         8.9       Temperature sensor       23         8.10       Oscillator Features       24         8.10.1       External Clock Source       24         8.10.2       External Clock Sourc                                                                   | U |      |                                        |    |

| 8.3       2-Wire-Serial Control and Data Bus (I <sup>2</sup> C Style Interface)       13         8.3.1       2-Wire Protocol Convention       14         8.3.2       2-Wire Vrite Operation       16         8.3.3       2-Wire Single Read Operation       16         8.4       2-Wire Timing       17         8.5       NAU7802 Streaming Data Mode       18         8.5.1       Enabling the Streaming I2C Mode       18         8.5.2       Streaming I2C Mode R/W Protocol 1       18         8.5.3       Streaming I2C Mode R/W Protocol 2       19         8.6       Device Calibration Features       20         8.6.1       Internal or External calibration       20         8.6.2       Calibration Error       21         8.6.3       Calibration Error       21         8.7       Internal Band-Gap Circuit       22         8.8       Reset and Power-down mode       22         8.9       Temperature sensor       23         8.10       Oscillator Features       24         8.10.1       External Cock Source       24         8.10.2       External Cock Source       24         8.10.1       External Cock Source       24         8.10.2       External Cock                                                                    |   | •••• |                                        |    |

| 8.3.1       2-Wire Protocol Convention       14         8.3.2       2-Wire Write Operation       16         8.3.3       2-Wire Single Read Operation       16         8.4       2-Wire Timing       17         8.5       NAU7802 Streaming Data Mode       18         8.5.1       Enabling the Streaming I2C Mode       18         8.5.2       Streaming I2C Mode R/W Protocol 1       18         8.5.3       Streaming I2C Mode R/W Protocol 2       19         8.6       Device Calibration Features       20         8.6.1       Internal or External calibration       20         8.6.2       Calibration Error       21         8.6.3       Calibration Error       21         8.6.3       Calibration Error       21         8.7       Internal Band-Gap Circuit       22         8.8       Reset and Power-down mode       22         8.9       Temperature sensor       23         8.10       Oscillator Features       24         8.10.1       External Clock Source       24         8.10.2       External Clock Source       24         8.10.2       External Clock Source       24         9       APPLICATION INFORMATION       25 <td></td> <td></td> <td></td> <td></td>                                                             |   |      |                                        |    |

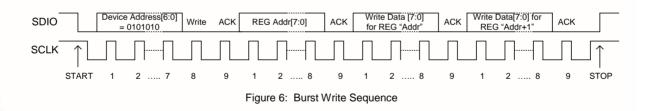

| 8.3.2       2-Wire Write Operation       16         8.3.3       2-Wire Single Read Operation       16         8.4       2-Wire Timing       17         8.5       NAU7802 Streaming Data Mode       18         8.5       NAU7802 Streaming I2C Mode       18         8.5.1       Enabling the Streaming I2C Mode       18         8.5.2       Streaming I2C Mode R/W Protocol 1       18         8.5.3       Streaming I2C Mode R/W Protocol 2       19         8.6       Device Calibration Features       20         8.6.1       Internal or External calibration       20         8.6.2       Calibration Features       20         8.6.3       Calibration Error       21         8.6.3       Calibration Error       21         8.7       Internal Band-Gap Circuit       22         8.8       Reset and Power-down mode       22         8.9       Temperature sensor       23         8.10       Oscillator Features       24         8.10.1       External Crystal Oscillator       24         8.10.2       External Clock Source       24         9       APPLICATION INFORMATION       25         9.1       Power-On Sequencing       25 </td <td></td> <td>0.0</td> <td></td> <td></td>                                                   |   | 0.0  |                                        |    |

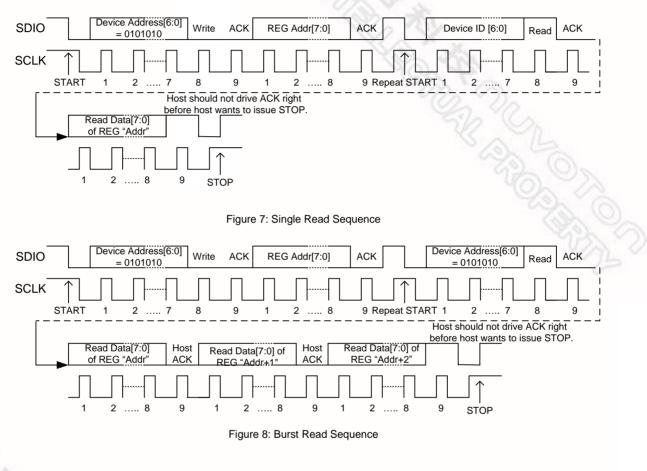

| 8.3.3       2-Wire Single Read Operation       16         8.4       2-Wire Timing.       17         8.5       NAU7802 Streaming Data Mode       18         8.5       NAU7802 Streaming I2C Mode       18         8.5.1       Enabling the Streaming I2C Mode       18         8.5.2       Streaming I2C Mode R/W Protocol 1       18         8.5.3       Streaming I2C Mode R/W Protocol 2       19         8.6       Device Calibration Features       20         8.6.1       Internal or External calibration       20         8.6.2       Calibration Error       21         8.6.3       Calibration Error       21         8.6.3       Calibration Error       21         8.6.4       Internal Band-Gap Circuit       22         8.7       Internal Band-Gap Circuit       22         8.8       Reset and Power-down mode       22         8.9       Temperature sensor       23         8.10       Oscillator Features       24         8.10.1       External Crystal Oscillator       24         8.10.2       External Clock Source       24         9       APPLICATION INFORMATION       25         9.1       Power-On Sequencing       25     <                                                                                            |   |      |                                        |    |

| 8.42-Wire Timing.178.5NAU7802 Streaming Data Mode188.5.1Enabling the Streaming I2C Mode188.5.2Streaming I2C Mode R/W Protocol 1188.5.3Streaming I2C Mode R/W Protocol 2198.6Device Calibration Features208.6.1Internal or External calibration208.6.2Calibration Limitations218.6.3Calibration Error218.7Internal Band-Gap Circuit228.8Reset and Power-down mode228.9Temperature sensor238.10Oscillator Features248.10.1External Crystal Oscillator248.10.2External Clock Source249APPLICATION INFORMATION259.1Power-On Sequencing259.2Signal path normal operation25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   |      |                                        |    |

| 8.5NAU7802 Streaming Data Mode188.5.1Enabling the Streaming I2C Mode188.5.2Streaming I2C Mode R/W Protocol 1188.5.3Streaming I2C Mode R/W Protocol 2198.6Device Calibration Features208.6.1Internal or External calibration208.6.2Calibration Limitations218.6.3Calibration Error218.7Internal Band-Gap Circuit228.8Reset and Power-down mode228.9Temperature sensor238.10Oscillator Features248.10.1External Crystal Oscillator248.10.2External Clock Source249APPLICATION INFORMATION259.1Power-On Sequencing259.2Signal path normal operation25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |   | 84   |                                        |    |

| 8.5.1Enabling the Streaming I2C Mode188.5.2Streaming I2C Mode R/W Protocol 1188.5.3Streaming I2C Mode R/W Protocol 2198.6Device Calibration Features208.6.1Internal or External calibration208.6.2Calibration Limitations218.6.3Calibration Error218.7Internal Band-Gap Circuit228.8Reset and Power-down mode228.9Temperature sensor238.10Oscillator Features248.10.1External Clock Source248.10.2External Clock Source249APPLICATION INFORMATION259.1Power-On Sequencing259.2Signal path normal operation25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   |      |                                        |    |

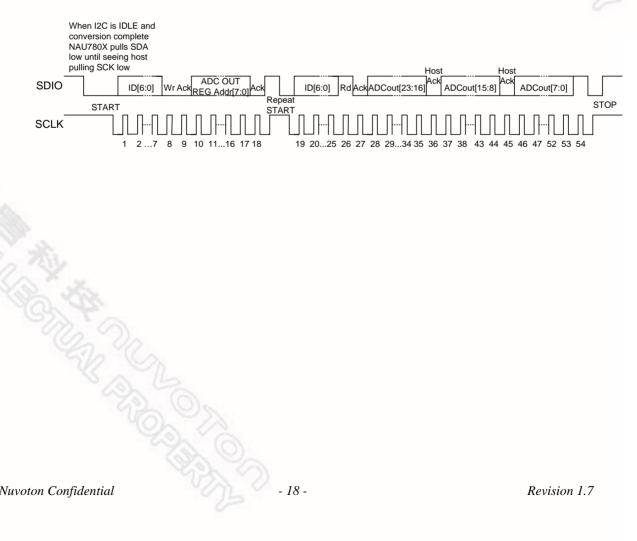

| 8.5.2Streaming I2C Mode R/W Protocol 1.188.5.3Streaming I2C Mode R/W Protocol 2.198.6Device Calibration Features.208.6.1Internal or External calibration.208.6.2Calibration Limitations.218.6.3Calibration Error.218.6.4Internal Band-Gap Circuit.228.7Internal Band-Gap Circuit.228.8Reset and Power-down mode.228.9Temperature sensor.238.10Oscillator Features.248.10.1External Crystal Oscillator.248.10.2External Clock Source.249APPLICATION INFORMATION.259.1Power-On Sequencing.259.2Signal path normal operation.25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   | 0.0  |                                        |    |

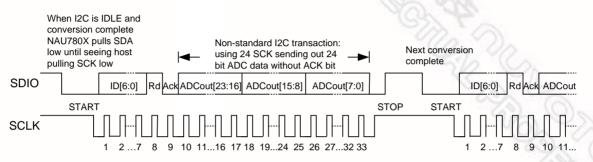

| 8.5.3Streaming I2C Mode R/W Protocol 2198.6Device Calibration Features208.6.1Internal or External calibration208.6.2Calibration Limitations218.6.3Calibration Error218.7Internal Band-Gap Circuit228.8Reset and Power-down mode228.9Temperature sensor238.10Oscillator Features248.10.1External Crystal Oscillator248.10.2External Clock Source249APPLICATION INFORMATION259.1Power-On Sequencing259.2Signal path normal operation25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |      |                                        |    |

| 8.6Device Calibration Features208.6.1Internal or External calibration208.6.2Calibration Limitations218.6.3Calibration Error218.7Internal Band-Gap Circuit228.8Reset and Power-down mode228.9Temperature sensor238.10Oscillator Features248.10.1External Crystal Oscillator248.10.2External Clock Source249APPLICATION INFORMATION259.1Power-On Sequencing259.2Signal path normal operation25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   |      | -                                      |    |

| 8.6.2Calibration Limitations218.6.3Calibration Error218.7Internal Band-Gap Circuit228.8Reset and Power-down mode228.9Temperature sensor238.10Oscillator Features248.10.1External Crystal Oscillator248.10.2External Clock Source249APPLICATION INFORMATION259.1Power-On Sequencing259.2Signal path normal operation25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   | 8.6  |                                        |    |

| 8.6.3Calibration Error218.7Internal Band-Gap Circuit228.8Reset and Power-down mode228.9Temperature sensor238.10Oscillator Features248.10.1External Crystal Oscillator248.10.2External Clock Source249APPLICATION INFORMATION259.1Power-On Sequencing259.2Signal path normal operation25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   |      | 8.6.1 Internal or External calibration | 20 |

| 8.7Internal Band-Gap Circuit228.8Reset and Power-down mode228.9Temperature sensor238.10Oscillator Features248.10.1External Crystal Oscillator248.10.2External Clock Source249APPLICATION INFORMATION259.1Power-On Sequencing259.2Signal path normal operation25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |   |      | 8.6.2 Calibration Limitations          | 21 |

| 8.8       Reset and Power-down mode       22         8.9       Temperature sensor       23         8.10       Oscillator Features       24         8.10       Oscillator Features       24         8.10.1       External Crystal Oscillator       24         8.10.2       External Clock Source       24         9       APPLICATION INFORMATION       25         9.1       Power-On Sequencing       25         9.2       Signal path normal operation       25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |      | 8.6.3 Calibration Error                | 21 |

| 8.9       Temperature sensor.       23         8.10       Oscillator Features.       24         8.10.1       External Crystal Oscillator.       24         8.10.2       External Clock Source.       24         9       APPLICATION INFORMATION       25         9.1       Power-On Sequencing.       25         9.2       Signal path normal operation       25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   | 8.7  | Internal Band-Gap Circuit              |    |

| 8.10       Oscillator Features       24         8.10.1       External Crystal Oscillator       24         8.10.2       External Clock Source       24         9       APPLICATION INFORMATION       25         9.1       Power-On Sequencing       25         9.2       Signal path normal operation       25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   | 8.8  | Reset and Power-down mode              |    |

| 8.10.1       External Crystal Oscillator       24         8.10.2       External Clock Source       24         9       APPLICATION INFORMATION       25         9.1       Power-On Sequencing       25         9.2       Signal path normal operation       25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   | 8.9  |                                        |    |

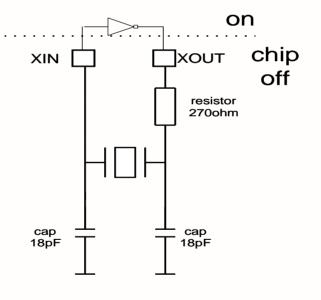

| 8.10.2       External Clock Source                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |   | 8.10 | Oscillator Features                    | 24 |

| 9       APPLICATION INFORMATION       25         9.1       Power-On Sequencing       25         9.2       Signal path normal operation       25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |   |      | 8.10.1 External Crystal Oscillator     | 24 |

| 9.1Power-On Sequencing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |   |      | 8.10.2 External Clock Source           | 24 |

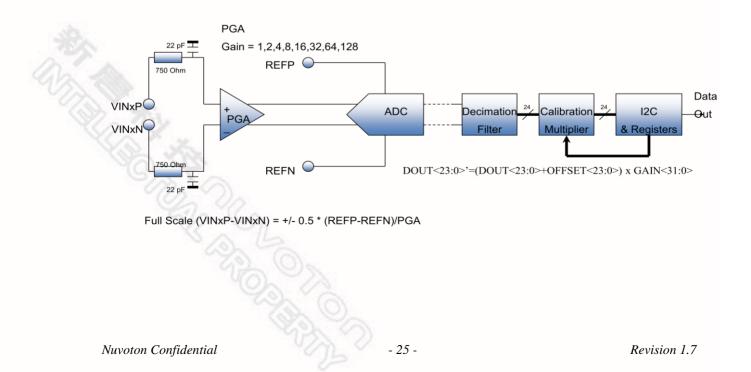

| 9.2 Signal path normal operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 9 | APPL | ICATION INFORMATION                    |    |

| 9.2 Signal path normal operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   | 9.1  | Power-On Sequencing                    |    |

| 5 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   | 9.2  |                                        |    |

| 9.3 Signal path with PGA bypass enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   | 9.3  | Signal path with PGA bypass enabled    |    |

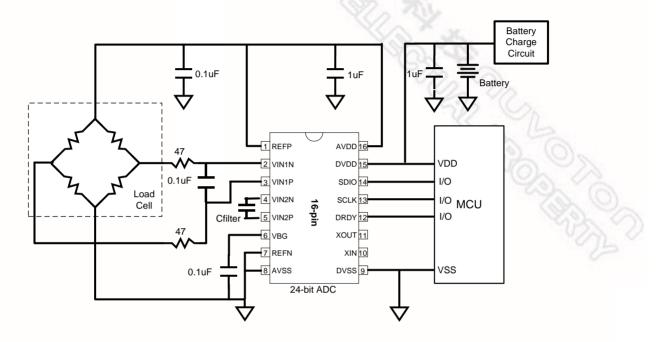

|        | 9.4 16-pin application circuit                                      | 27    |

|--------|---------------------------------------------------------------------|-------|

| 10     | SUMMARY DEVICE REGISTER MAP                                         | 28    |

| 11     | DEVICE REGISTER MAP DETAILS                                         | 29    |

|        | 11.1 REG0x00:PU_CTRL                                                | 29    |

|        | 11.2 REG0x01:CTRL1                                                  |       |

|        | 11.3 REG0x02:CTRL2                                                  |       |

|        | 11.4 REG0x03-REG0x05: Channel 1 OFFSET Calibration                  |       |

|        | 11.5 REG0x06-REG0x09: Channel 1 GAIN Calibration                    | 32    |

|        | 11.6 REG0x0A-REG0x0C: Channel 2 OFFSET Calibration (NAU7802 - only) | 32    |

|        | 11.7 REG0x0D-REG0x10: Channel 2 GAIN Calibration (NAU7802 - only)   |       |

|        | 11.8 REG0x11: I2C Control                                           | 33    |

|        | 11.9 REG0x12-REG0x14: ADC Conversion Result                         | 34    |

|        | 11.10 REG0x15: ADC registers                                        |       |

|        | REG0x15-REG0x17: OTP Read Value and REG0x15 ADC Registers Read      |       |

|        | 11.11 REG0x18: Read Only                                            |       |

|        | 11.12 REG0x19: Read Only                                            |       |

|        | 11.13 REG0x1A: Read Only                                            |       |

|        | 11.14 REG0x1B: PGA Registers                                        |       |

|        | 11.15 REG0x1C: POWER CONTROL Register                               |       |

|        | 11.15.1 REG0x1D: Read Only                                          |       |

|        | 11.15.2 REG0x1E: Read Only                                          |       |

|        | 11.15.3 REG0x1F: Read Only                                          | 37    |

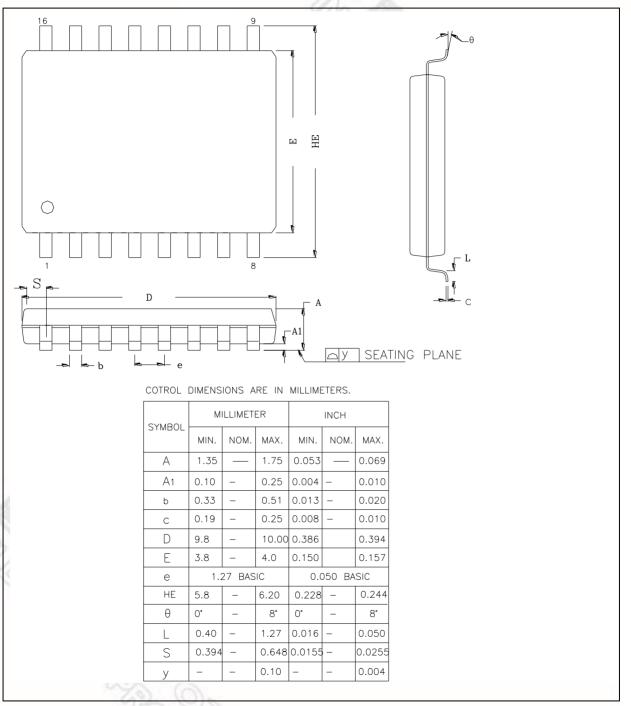

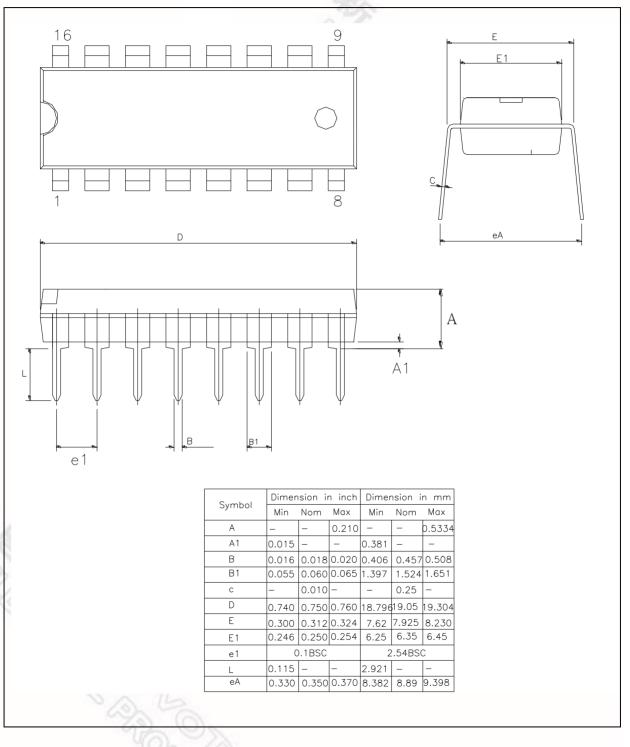

| 12     | PACKAGE DIMENSIONS                                                  | 38    |

|        | 12.1 16L SOP – 150 mil                                              | 38    |

|        | 12.2 PDIP16L - 300 mil                                              | 39    |

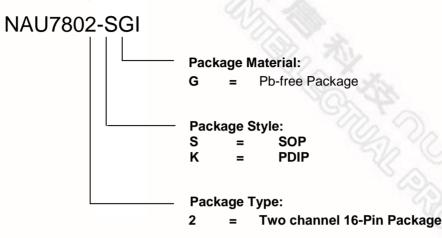

| 13     | PART ORDERING INFORMATION                                           | 40    |

| 14     | REVISION HISTORY                                                    | 41    |

|        |                                                                     |       |

|        |                                                                     |       |

|        |                                                                     |       |

|        |                                                                     |       |

|        |                                                                     |       |

|        |                                                                     |       |

|        |                                                                     |       |

|        |                                                                     |       |

|        |                                                                     |       |

|        |                                                                     |       |

|        |                                                                     |       |

|        |                                                                     |       |

|        |                                                                     |       |

|        |                                                                     |       |

|        |                                                                     |       |

|        |                                                                     |       |

|        |                                                                     |       |

| Ŋ      |                                                                     | 17    |

| Nuvoto | n Confidential - 3 - Revision                                       | ı I.7 |

|        |                                                                     |       |

|        |                                                                     |       |

|        |                                                                     |       |

#### 1 **GENERAL DESCRIPTION**

The Nuvoton NAU7802 is a precision low-power 24-bit analog-to-digital converter (ADC), with an onboard low-noise programmable gain amplifier (PGA), onboard RC or Crystal oscillator, and a precision 24-bit sigma-delta ( $\Sigma$ - $\Delta$ ) analog to digital converter (ADC). The NAU7802 device is capable of up to 23-bit ENOB (Effective Number Of Bits) performance. This device provides a complete front-end solution for bridge/sensor measurement such as in weigh scales, strain gauges, and many other high resolution. low sample rate applications.

The many built-in features enable high performance applications with very low external parts count. Additionally, both operating current and standby current are very low, and many power management features are included. These enable powering only those elements of the chip that are needed, and also, to operate at greatly reduced power if the full 23-bit ENOB performance is not required.

The Programmable Gain Amplifier (PGA) provides selectable gains from 1 to 128. The A/D conversion is performed with a Sigma-Delta modulator and programmable FIR filter that provides a simultaneous 50Hz and 60Hz notch filter to effectively improve interference immunity. Also, this device provides a standard 2-wire interface compatible with I2C protocol for simple and straightforward connection to and interoperation with a wide range of possible host processors.

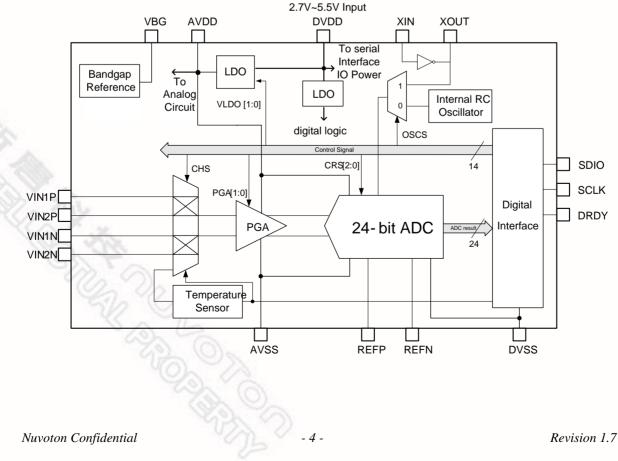

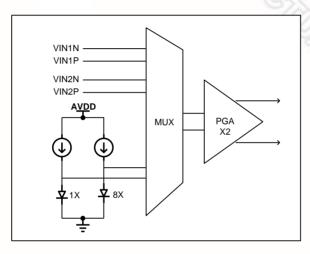

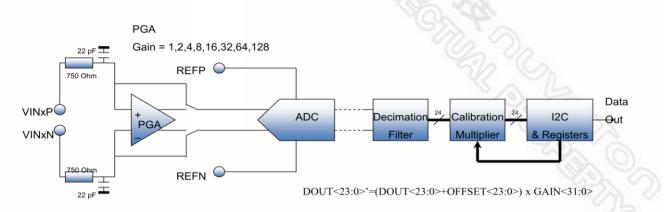

#### 2 SYSTEM BLOCK DIAGRAM

#### **3 FEATURES**

- Supply power: 2.7V~5.5V

- On-chip VDDA regulator for internal analog circuit or external load cell

- Programmable VDDA: Off, 2.4V to 4.5V with eight options

- Minimum 10mA output drive capability at 3.0V output voltage

- Note: DVDD must be 0.3Vdc greater than desired VDDA output voltage

- 23 bits effective precision analog-to-digital converter

- Simultaneous 50Hz and 60Hz rejection (reaching -90dB)

- RMS Noise:

- 50nV in 10 SPS data output rate and PGA gain = 128

- 150nV in 80 SPS data output rate and PGA gain = 128

- Programmable PGA gains from 1 to 128

- Programmable ADC data output rates

- External differential reference voltage range from 0.1V to 5V

- System clock: External crystal oscillator or on-chip RC oscillator (4.9152Mhz)

- On-chip calibration

- On-chip power-on reset circuit

- On-chip temperature sensor

- Low Power Consumption and Programmable Power Management Options

- I < 1uA standby current</p>

- External 4.9152MHz Crystal oscillator

- System clock:

- Internal 4.9152MHz RC oscillator (power-on default system clock)

- External 4.9152MHz Crystal oscillator

- MCU control interface: 2-wire interface compatible with I2C protocol

- Operating Temperature: -40~85C

- Packages:

- SOP-16 (150mil) / PDIP-16

### **APPLICATIONS**

- Weigh scales

- Strain Gauge

- Industrial process control

- Liquid/gas flow control

- Pressure sensors

- Voltage monitors

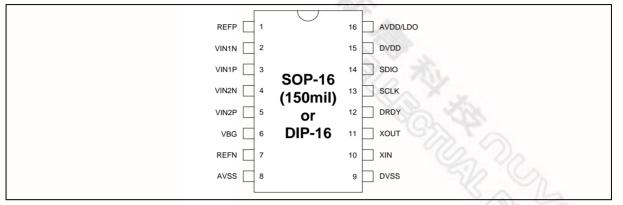

#### **PIN CONFIGURATION** 5

#### 6 **PIN DESCRIPTION**

| Pin No. | Pin Name | Туре | DESCRIPTIONS                                                                                                                                                                           |

|---------|----------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | REFP     | AI   | Positive reference input                                                                                                                                                               |

| 2       | VIN1N    | AI   | Inverting Input #1                                                                                                                                                                     |

| 3       | VIN1P    | AI   | Non-Inverting Input #1                                                                                                                                                                 |

| 4       | VIN2N    | AI   | Inverting Input #2                                                                                                                                                                     |

| 5       | VIN2P    | AI   | Non-Inverting Input #2                                                                                                                                                                 |

| 6       | VBG      | Α    | High impedance Reference Voltage Output and Bypass                                                                                                                                     |

| 7       | REFN     | AI   | Negative Reference Input                                                                                                                                                               |

| 8       | AVSS     | Р    | Analog Ground                                                                                                                                                                          |

| 9       | DVSS     | Р    | Digital ground                                                                                                                                                                         |

| 10      | XIN      | I    | External crystal oscillator input. Typically 4.9152 MHz                                                                                                                                |

| 11      | XOUT     | 0    | External crystal oscillator output.                                                                                                                                                    |

| 12      | DRDY     | 0    | Data Ready Output indicating a conversion is complete and new data are available for readout. (CMOS Driver high / low                                                                  |

| 13      | SCLK     | I    | Serial Data Clock Input (CMOS open drain output)                                                                                                                                       |

| 14      | SDIO     | I/O  | Data Input / Output for serial communication with host (CMOS open drain output)                                                                                                        |

| 15      | DVDD     | Р    | Digital power supply: 2.7V ~ 5.5V                                                                                                                                                      |

| 16      | AVDD/LDO | P    | <ul> <li>Analog power supply:</li> <li>1. From programmable LDO output, low ESR 1 ohm or lest capacitor recommended</li> <li>2. LDO off: external power supply: 2.7V ~ 5.5V</li> </ul> |

• Note : TYPE P: Power, AI: Analog input, AO: Analog output, I: input, O: output, I/O: bi-directional

#### 7 **ELECTRICAL CHARACTERISTICS**

#### 7.1 **Absolute Maximum Ratings**

| SYMBOL                | PARAMETER        | CONDITION               | MINIMUM | MAXIMUM    | UNIT |

|-----------------------|------------------|-------------------------|---------|------------|------|

|                       | DVDD             | DVDD-DVSS               | -0.3    | +6.0       | V    |

| DC Power Supply       | AVDD*            | AVDD-AVSS               | -0.3    | +6.0       | V    |

|                       | AVSS-DVSS        | -                       | -0.3    | +0.3       | V    |

| Analog Input Voltage  | AV <sub>IN</sub> | AV <sub>IN</sub> – AVSS | -0.3    | AVDD + 0.3 | V    |

| Digital input Voltage | DV <sub>IN</sub> | DV <sub>IN</sub> – DVSS | -0.3    | DVDD + 0.3 | V    |

| Operating Temperature | ТА               |                         | -40     | +85        | °C   |

| Storage Temperature   | Tst              |                         | -55     | +150       | °C   |

Note: Exposure to conditions beyond those listed under absolute maximum ratings may adversely affects the life time and reliability

\* AVDD should not exceed DVDD supply voltage

#### **DC ELECTRICAL CHARACTERISTICS** 7.2

(Unless otherwise specified; Typical value is tested at TA=25°C, DVDD = 5V, AVDD = 5V)

| PARAMETER          |      | SPECI | FICATION  | TEST CONDITIONS |                                                                                                 |  |

|--------------------|------|-------|-----------|-----------------|-------------------------------------------------------------------------------------------------|--|

|                    | MIN. | TYP.  | MAX. UNIT |                 |                                                                                                 |  |

| POWER SUPPLY       |      |       |           |                 |                                                                                                 |  |

| Operating Voltage  | 2.7  |       | 5.5       | V               | DVDD                                                                                            |  |

| Operating Voltage  | 2.7  |       | DVDD      | V               | AVDD                                                                                            |  |

| Operating Current  |      | 2.1   |           | mA              | Internal OSC & LDO                                                                              |  |

| Operating Current  |      | 2     |           | mA              | Internal OSC, no LDO                                                                            |  |

| Power Down Current |      | 0.2   | 1         | μΑ              | All analog part include internal RC<br>oscillator or external crystal<br>oscillator. PUA =PUD=0 |  |

|                    |      |       |           |                 |                                                                                                 |  |

|                    |      |       |           |                 |                                                                                                 |  |

| (VINxP – VINxN)                           | ±0            | .5/(VREF/P | GA)           | V               | VREF = REFP – REFN                                   |

|-------------------------------------------|---------------|------------|---------------|-----------------|------------------------------------------------------|

| Common mode range with PGA gain 64, 128   | AVSS +<br>1.5 |            | AVDD -<br>1.5 | v               |                                                      |

| Common mode range with PGA bypass enabled | AVSS -<br>0.1 |            | AVDD +<br>0.1 | v               |                                                      |

| Differential input impedance              |               | 5          |               | GΩ              | PGA bypass=off, DC                                   |

| Pondwidth (2dP)                           |               | 2.27       |               | Hz              | Data output rate = 10 SPS                            |

| Bandwidth (-3dB)                          |               | 18.17      |               | Hz              | Data output rate = 80 SPS                            |

| PGA                                       | 1             |            | 128           | 1               | User-selectable gain range                           |

| Input capacitance channel 1               |               | 14         |               | pF              | Ne Sp                                                |

| Input capacitance channel 2               |               | 5          |               | pF              | No. E                                                |

| Differential Input leakage current        |               | 20         |               | рА              | PGA bypass=off                                       |

| Burnout current sources                   |               | 2.5        |               | μA              |                                                      |

| SYSTEM PERFORMANCE                        | ·             |            |               |                 | 292 6                                                |

| Resolution                                |               | 24         |               |                 | No missing codes                                     |

| Integral nonlinearity NAU7802             |               | ± 0.0015   |               | % of FS         | With calibration                                     |

| Offset error                              |               | +/-0.3     |               | ppm of FS       | With calibration, 1024 sample                        |

| Offset error drift                        |               | 0.02       |               | ppm of<br>FS/°C | With calibration                                     |

| Gain error                                |               | 0.01       |               | %               | With calibration                                     |

| Gain error drift                          |               | 1          |               | ppm/°C          | With calibration                                     |

|                                           | 96            | 100        |               | dB              | at DC 2.5 V ± 0.5 V                                  |

| Common-mode rejection                     |               | 130        |               | dB              | $f_{CM} = 60$ Hz, 500 mVpp<br>ADC data rate = 10 SPS |

|                                           |               | 120        |               | dB              | $f_{CM} = 50$ Hz, 500 mVpp<br>ADC data rate = 10 SPS |

| Notoh rojection                           |               | 100        |               | dB              | $f_{CM} = 60$ Hz, 500 mVpp<br>ADC data rate = 10 SPS |

| Notch rejection                           |               | 100        |               | dB              | $f_{CM} = 50$ Hz, 500 mVpp<br>ADC data rate = 10 SPS |

| Power supply rejection                    | 96            | 100        |               | dB              | at DC 5 V $\pm$ 0.25 V, with LDO                     |

| VOLTAGE REFERENCE INPUT                   |               |            |               |                 |                                                      |

| VREF = REFP - REFN                        | 1.5           | AVDD       | AVDD+.<br>0.1 | V               |                                                      |

| REFN input range                          | -0.1          |            | VREFP-<br>1.5 | V               |                                                      |

| REFP input range                          | VREFN+<br>1.5 |            | AVDD+<br>0.1  |                 |                                                      |

| 90.90                                     | VREFN+        |            | AVDD+         |                 |                                                      |

| Nuvoton Confidential                      |               | - 8        | -             |                 | Revision 1.7                                         |

| DIGITAL SERIAL INTERFACE                                           |             |      | . 335       | 6   |                                                                                |

|--------------------------------------------------------------------|-------------|------|-------------|-----|--------------------------------------------------------------------------------|

| Input Leakage Current SCK, SI                                      | -1          | -    | +1          | μA  | $DVDD = 5.5V, 0 < V_{IN} < DVDD$                                               |

| Input High Voltage VIH                                             | 0.7 VDD     |      | 5.5         | V   |                                                                                |

| Input low Voltage VIL                                              | DVSS        |      | 0.3 VDD     | V   |                                                                                |

| VOH (DRDY)                                                         | 0.9<br>DVDD |      | No.         | v   | IOH = 1 mA                                                                     |

| VOH (SCLK, SDIO)                                                   | 0.9<br>DVDD |      |             | V   | Defined by pull up resistor.<br>(Internal weak, internal strong,<br>external.) |

| VOL (SCLK, SDIO, DRDY)                                             |             |      | 0.2<br>DVDD | V   | IOL = 1 mA                                                                     |

| SDIO pull-up resistor Input High<br>Voltage P1, P2, P3 (TTL input) |             | DVDD |             | V   | V <sub>DD</sub> = 5.5V                                                         |

| SDIO, SCLK; pull up resistor value                                 | 1.6 k       | 50 k | none        | Ohm | Selectable; strong, weak, none                                                 |

| Power On Reset Voltage                                             |             | 1.6  |             | V   |                                                                                |

### 7.3 RC OSC AND AC CHARACTERISTICS

| Parameter                                                                                        | Specification (reference) |      |      |      | Test Conditions                                        |

|--------------------------------------------------------------------------------------------------|---------------------------|------|------|------|--------------------------------------------------------|

| Falameter                                                                                        | Min.                      | Тур. | Max. | Unit |                                                        |

| 4.9152 MHz On-chip RC oscillator                                                                 |                           | +/-3 |      | %    | DVDD = 5V, T=25C; NAU7802 only                         |

| T <sub>RDY</sub> : Analog part wakeup stable plus<br>Data Ready after exiting power-down<br>mode |                           | 600  |      | ms   | DVDD = 5V; at 10 S/sec<br>(5 sample times plus 100 ms) |

### 7.4 TEMPERATURE SENSOR

| Parameter                            | Sp   | pecification | n (referenc | Test Conditions |                  |

|--------------------------------------|------|--------------|-------------|-----------------|------------------|

| Farameter                            | Min. | Тур.         | Max.        | Unit            |                  |

| Temperature sensor output            |      | 109          |             | mV              | at 25°C          |

| Temperature sensor delta coefficient |      | 360          |             | uV / °C         | relative to 25°C |

#### **Typical Characteristic** 7.5

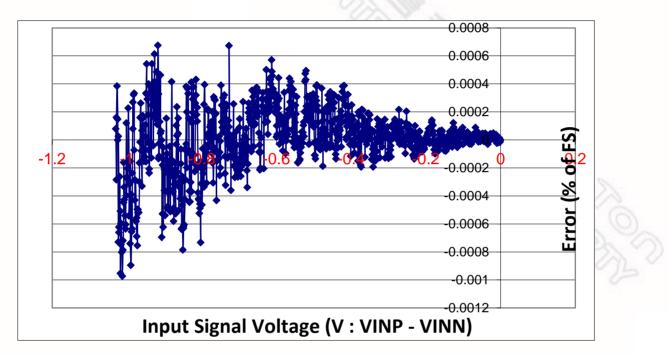

7.5.1 NAU7802 Linearity – (Error % vs. Input Voltage) AVDD = 4.5V / PGA gain = 1x

NAU7802 Linearity Performance is symmetric, from the differential input voltage -1.2V to 0V . and from 0V to 1.2V. One-sided linearity performance result is shown.

#### 7.5.2 Noise Performance – NAU7802

| AVDD/<br>REFP (V) | PGA<br>Gain | ENOB  | ENOB2 | NOISE_FREE_BITS |  |  |  |  |

|-------------------|-------------|-------|-------|-----------------|--|--|--|--|

| 4.5               | 1           | 22.29 | 22.31 | 20.09           |  |  |  |  |

| 4.5               | 2           | 22.15 | 22.16 | 19.75           |  |  |  |  |

| 4.5               | 4           | 22.01 | 22.02 | 19.61           |  |  |  |  |

| 4.5               | 8           | 21.88 | 21.91 | 19.36           |  |  |  |  |