# 802.11b/g/n WICED Module (WM-N-BM-14)

Datasheet July 24 2013 Rev 2.3

www.usi.com.tw

# **Datasheet**

# of

# WM-N-BM-14 WICED Module

#### Introduction

The WM-N-BM-14 wireless WICED module which is a small size module and consists of a Broadcom BCM43362 single-chip, a ST STM32F205RG MCU, and a 2.4G antenna. The WM-N-BM-14 provides for the highest-level integration, featuring 802.11b/g and 802.11n.

It includes a 2.4 GHz WLAN CMOS power amplifier (PA) that meets the output power requirements of most handheld systems. An optional external low-noise amplifier (LNA) and external PA are also supported. Along with the integrated power amplifier, the WM-N-BM-14 also includes integrated transmit and receive baluns, further reducing the overall solution cost.

The small size & low profile physical design make it easier for system design to enable high performance wireless connectivity without space constrain. This multi- functionality and board to board physical interface provides SPI/I2C/I2S/UART interface options.

Hardware WAPI acceleration engine, AES, TKIP, WPA and WPA2 are supported to provide the latest security requirement on your network.

For the software and driver development, USI provides extensive technical document and reference software code for the system integration under the agreement of Broadcom International Ltd.

Hardware evaluation kit and development utilities will be released base on listed OS and processors to OEM customers.

#### **Features**

#### **BCM43362 Wi-Fi**

- Single band 2.4GHz IEEE 802.11b/g/n

- Supports wireless data rates up to 65Mbit/s

- Integrated RF power amplifier

#### STM32F205RGY6 Microprocessor

- ARM 32-bit Cortex-M3 CPU

- CPU frequency up to 120MHz

- 1 MB Flash memory

- 128 kB SRAM

- Low-power sleep, standby and stop modes

- Extend one 8Mbit Flash memory

#### WM-N-BM-14 Wireless Module

- Featuring integrated IEEE 802.11 b/g/n

- Supports per packet Rx Antenna diversity

- Low power consumption & excellent power management performance extend battery life.

- Small size suitable for low volume system integration.

- Easy for integration into mobile and handheld device with flexible system configuration.

- 2.412-2.484 GHz two SKUs for worldwide market.

- Lead Free design which supporting Green design requirement, RoHS Compliance.

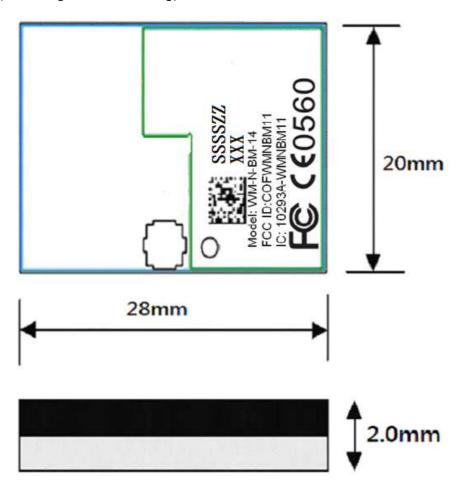

## **Device Package**

28x20 mm

|      | Change Sheet |         |     |                                                                      |                 |  |  |

|------|--------------|---------|-----|----------------------------------------------------------------------|-----------------|--|--|

| Rev. |              |         |     |                                                                      | Approval & Date |  |  |

|      |              | Page    | Par | Change(s)                                                            |                 |  |  |

| 1.1  | 01/15/13     | All     | All | Initial Release                                                      | Scarrie/Kevin   |  |  |

|      |              | 2       |     | Update module picture in Introduction                                |                 |  |  |

| 2.1  | 07/10/13     | 12      | 5.5 | Add power table of band eange-regulatory for US/Canada and EU market | Scarrie/Kevin   |  |  |

|      |              | 24      | 10  | Update recommend footprint dimension                                 |                 |  |  |

| 2.2  | 07/18/13     | 19      | 9.1 | Update the picture of module dimension                               | Scarrie         |  |  |

| 2.3  | 07/24/13     | 25 ~ 27 | 12  | UPDATE PACKAGE AND STORAGE CONDITION                                 | Scarrie         |  |  |

|      |              |         |     |                                                                      |                 |  |  |

|      |              |         |     |                                                                      |                 |  |  |

|      |              |         |     |                                                                      |                 |  |  |

|      |              |         |     |                                                                      |                 |  |  |

|      |              |         |     |                                                                      |                 |  |  |

#### **TABLE OF CONTENTS**

| 1  | EXECUTIVE SUMMARY                                                                                                                                                                                                                                                                             | 5                       |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

| 2  | BLOCK DIAGRAM                                                                                                                                                                                                                                                                                 | 6                       |

| 3  | DELIVERABLES                                                                                                                                                                                                                                                                                  |                         |

| 4  | REFERENCE DOCUMENTS                                                                                                                                                                                                                                                                           | 8                       |

| 5  | TECHNICAL SPECIFICATION                                                                                                                                                                                                                                                                       | 9                       |

|    | 5.1 ABSOLUTE MAXIMUM RATING 5.2 RECOMMENDABLE OPERATION CONDITION 5.2.1 TEMPERATURE, HUMIDITY 5.2.2 VOLTAGE 5.2.3 CURRENT CONSUMPTION 5.4 SPECIFICATIONS OF WIFI'S OUTPUT POWER \ EVM \ SENSITIVITY 5.5 SPECIFICATIONS OF WIFI'S BAND EANGE-REGULATORY POWERTABLE FOR US/CANADA AND EU MARKET | 9<br>9<br>9<br>10<br>11 |

| 6  | FLASH MEMORY                                                                                                                                                                                                                                                                                  | 13                      |

|    | 6.1 MCU EMBEDDED FLASH MEMORY                                                                                                                                                                                                                                                                 | 13<br>13                |

| 7  | I/O PORT CHARACTERISTICS                                                                                                                                                                                                                                                                      | 14                      |

| 8  | COMMUNICATIONS INTERFACE                                                                                                                                                                                                                                                                      | 15                      |

| 9  | DIMENSIONS, WEIGHT AND MOUNTING                                                                                                                                                                                                                                                               | 18                      |

| 1( | RECOMMEND FOOTPRINT                                                                                                                                                                                                                                                                           | 23                      |

| 1  | 1 RECOMMEND REFLOW PROFILE                                                                                                                                                                                                                                                                    | 24                      |

| 12 | PACKAGE AND STORAGE CONDITION                                                                                                                                                                                                                                                                 | 25                      |

| 1; | 3 ESD LEVEL                                                                                                                                                                                                                                                                                   | 28                      |

| 4  | MOLLEVEL / STORAGE CONDITION                                                                                                                                                                                                                                                                  | 20                      |

#### 1 EXECUTIVE SUMMARY

The WM-N-BM-14 module - is one of the product families in UG's product offering, targeting for system integration requiring a smaller form factor. It also provides the standard migration to high data rate to UG's current SIP customers.

The purpose of this document is to define the product specification for 802.11b/g/n WiFi module WM-N-BM-14. All the data in this document is based on Broadcom 43362 datasheet, STM32F205 datasheet and other documents provided from Broadcom and ST . The data will be updated after implementing the measurement of the module.

#### 2 BLOCK DIAGRAM

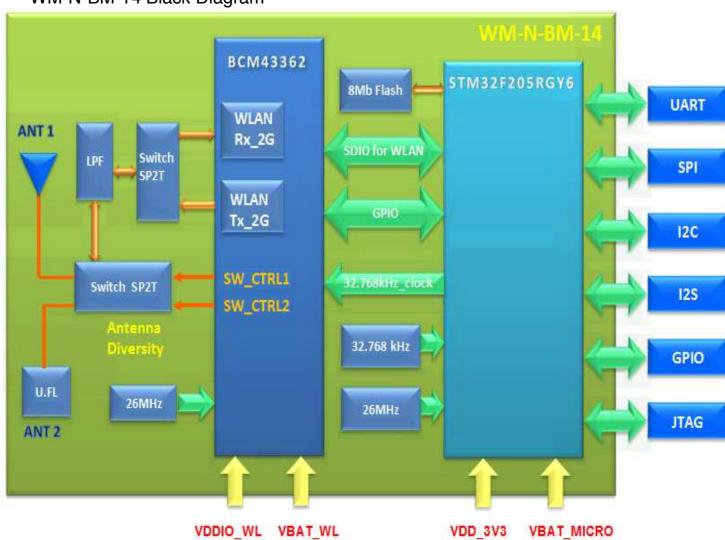

The WM-N-BM-14 module is designed based on Broadcom 43362 chipset and ST MCU solution. It supports generic SPI, UART, I2S, I2C interface to connect the WLAN to the host processor. A simplified block diagram of the WM-N-BM-14 module is depicted in the Fig. below.

WM-N-BM-14 Black Diagram

This document is controlled and confidential under the terms of USI

6

#### 3 DELIVERABLES

The following products and software will be part of the product.

- WM-N-BM-14 Module with packaging

- Evaluation kits (with SPI / UART/ JTAG interface)

- Software utility which supporting customer for integration, performance test and homologation. Capable of testing, loading (firmware) and configuring (MAC, CIS) for the WM-N-BM-14 module.

- Unit Test / Qualification report

- Product Specifications.

- Agency certification pre-test report base on adapter boards

## **4 REFERENCE DOCUMENTS**

| C.I.S.P.R.<br>Pub. 22   | "Limits and methods of measurement of radio interference characteristics of information technology equipment." International Special Committee on Radio Interference (C.I.S.P.R.), Third Edition, 1997.                                                                                   |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CB Bulletin<br>No. 96A  | "Adherence to IEC Standards: "Requirements for IEC 950, 2 <sup>nd</sup> Edition and Amendments 1 (1991), 2(1993), 3 (1995) and 4(1996). Product Categories: Meas, Med, Off, Tron." IEC System for Conformity Testing to Standards for Safety of Electrical Equipment (IECEE), April 2000. |

| CFR 47,<br>Part 15-B    | "Unintentional Radiators". Title 47 of the Code of Federal Regulations, Part 15, FCC Rules, Radio Frequency Devices, Subpart B.                                                                                                                                                           |

| CFR 47,<br>Part 15-C    | "Intentional Radiators". Title 47 of the Code of Federal Regulations, Part 15, FCC Rules, Subpart C. URL: <a href="http://www.access.gpo.gov/nara/cfr/waisidx_98/47cfr15_98.html">http://www.access.gpo.gov/nara/cfr/waisidx_98/47cfr15_98.html</a>                                       |

| CSA C22.2<br>No. 950-95 | "Safety of Information Technology Equipment including Electrical Business Equipment, Third Edition." Canadian Standards Association, 1995, including revised pages through July 1997.                                                                                                     |

| EN 60 950               | "Safety of Information Technology Equipment Including Electrical Business Equipment." European Committee for Electrotechnical Standardization (CENELEC), 1996, (IEC 950, Second Edition, including Amendment 1, 2, 3 and 4).                                                              |

| IEC 950                 | "Safety of Information Technology Equipment Including Electrical Business Equipment." European Committee for Electrotechnical Standardization, Intentional Electrotechnical Commission. 1991, Second Edition, including Amendments 1, 2, 3, and 4.                                        |

| IEEE 802.11             | "Wireless LAN Medium Access Control (MAC) And Physical Layer (PHY) Specifications." Institute of Electrical and Electronics Engineers. 1999.                                                                                                                                              |

#### 5 TECHNICAL SPECIFICATION

#### 5.1 ABSOLUTE MAXIMUM RATING

| Supply Power              | Max +3.6 Volt        |                                     |

|---------------------------|----------------------|-------------------------------------|

| Non Operating Temperature | - 40° to 85° Celsius |                                     |

| Voltage ripple            | +/- 2%               | Max. Values not exceeding Operating |

|                           |                      | voltage                             |

#### 5.2 RECOMMENDABLE OPERATION CONDITION

#### **5.2.1 TEMPERATURE, HUMIDITY**

The WM-N-BM-14 module has to withstand the operational requirements as listed in the table below.

| Operating Temperature | -20° to 75° Celsius |                                   |

|-----------------------|---------------------|-----------------------------------|

| Humidity range        | Max 95%             | Non condensing, relative humidity |

<sup>\*</sup> The maximum operating ambient temperature range can up to 85degC, but exposure to absolute-maximum-rated conditions may cause performance degradation and affect device reliability.

#### 5.2.2 VOLTAGE

Power supply for the WM-N-BM-14 module will be provided by the host via the power pins

| <u> </u>     |                             |     | <u> </u> |     |      |

|--------------|-----------------------------|-----|----------|-----|------|

| Symbol       | Parameter                   | Min | Тур.     | Max | Unit |

| VBAT_WL      | power supply for BCM43362   | 3.0 | 3.3      | 3.6 | V    |

| VDDIO_3V3_WL | host Interface power supply | 3.0 | 3.3      | 3.6 | V    |

| VBAT_MICRO   | backup operating voltage    | 3.0 | 3.3      | 3.6 | V    |

| VDD_3V3      | power supply for MCU        | 3.0 | 3.3      | 3.6 | V    |

#### **5.2.3 CURRENT CONSUMPTION**

The WM-N-BM-14 on TX mode output current consumption :

(Typical spec is defined @3.3V 25°C; MAX. spec is defined @3.0V 70°C)

| Current Consumption                    | TYP.   | MAX.   |

|----------------------------------------|--------|--------|

| Tx output power @16.5 dBm on 11b 1M    | 385 mA | 430 mA |

| Tx output power @ 16.5 dBm on 11b 11M  | 370 mA | 410 mA |

| Tx output power @ 15 dBm on 11g 6M     | 345 mA | 380 mA |

| Tx output power @ 13 dBm on 11g 54M    | 290 mA | 320 mA |

| Tx output power @ 14.5 dBm on 11n MCS0 | 315 mA | 350 mA |

| Tx output power @ 12 dBm on 11n MCS7   | 265 mA | 295 mA |

This document is controlled and confidential under the terms of USI

9

The WM-N-BM-14 on RX mode current consumption :

(Typical spec is defined @3.3V 25°C; MAX. spec is defined @3.0V 70°C)

| Current Consumption | TYP.   | MAX.   |

|---------------------|--------|--------|

| Rx @ 11b 1M         | 120 mA | 150 mA |

| Rx @ 11b 11M        | 120 mA | 150 mA |

| Rx @ 11g 6M         | 120 mA | 150 mA |

| Rx @ 11g 54M        | 120 mA | 150 mA |

| Rx @ 11n MCS0       | 120 mA | 150 mA |

| Rx @ 11n MCS7       | 120 mA | 150 mA |

#### 5.3 WIRELESS SPECIFICATIONS

The WM-N-BM-14 module complies with the following features and standards;

| Features               | Description                                                  |

|------------------------|--------------------------------------------------------------|

| WLAN Standards         | IEEE 802 11 b/g/n                                            |

| Antenna Connecter Port | One printed antenna, one U.FL connector for external antenna |

| Frequency Band         | 2.400 GHz – 2.484 GHz                                        |

| Number of Sub Channels | CH1 to CH14                                                  |

| Modulation             | DSSS, CCK, OFDM, BPSK, QPSK,16QAM, 64QAM                     |

| Supported data rates   | 11b 1, 2, 5.5, 11 (Mbps)                                     |

|                        | 11g 6, 9, 12, 18, 24, 36, 48, 54 (Mbps)                      |

|                        | 11n HT20 MCS0(6.5Mbps) to HT20 MCS7(65Mbps)                  |

#### 5.4 SPECIFICATIONS OF WIFI'S OUTPUT POWER . EVM . SENSITIVITY

The WM-N-BM-14 module WiFi output power as list in the table below:

| Characteristics                            |      | TYP. | Criteria | Unit |

|--------------------------------------------|------|------|----------|------|

|                                            | 1M   | 16.5 | +/- 1.5  | dBm  |

| RF Average Output Power, 802.11b CCK Mode  | 11M  | 16.5 | +/- 1.5  | dBm  |

|                                            | 6M   | 15   | +/- 1.5  | dBm  |

| RF Average Output Power, 802.11g OFDM Mode | 54M  | 13   | +/- 1.5  | dBm  |

|                                            | MCS0 | 14.5 | +/- 1.5  | dBm  |

| RF Average Output Power, 802.11n OFDM Mode | MCS7 | 12   | +/- 1.5  | dBm  |

WiFi TX EVM follow the IEEE spec that as list in the table below:

| Characteristics                 | IEEE Spec | Unit |    |

|---------------------------------|-----------|------|----|

| RF Average Output EVM (11b)     | @1 Mbps   | -10  | dB |

| Average Output Evivi (11b)      | @11 Mbps  | -10  | dB |

| DE Average Output EVM (11a)     | @6 Mbps   | -5   | dB |

| RF Average Output EVM (11g)     | @54 Mbps  | -25  | dB |

| RF Average Output EVM (11n)     | @ MCS0    | -5   | dB |

| The Average Output Evivi (Till) | @ MCS7    | -28  | dB |

The WM-N-BM-14 module WiFi sensitivity as list in the table below:

| Receiver Characteristics           | TYP. | MAX. | Unit |

|------------------------------------|------|------|------|

| PER <8%, Rx Sensitivity @ 1 Mbps   | -96  | -89  | dBm  |

| PER <8%, Rx Sensitivity @ 11 Mbps  | -88  | -84  | dBm  |

| PER <10% Rx Sensitivity @ 6 Mbps   | -90  | -83  | dBm  |

| PER <10%, Rx Sensitivity @ 54 Mbps | -74  | -70  | dBm  |

| PER <10%, Rx Sensitivity @ MCS0    | -89  | -83  | dBm  |

| PER <10%, Rx Sensitivity @ MCS7    | -71  | -67  | dBm  |

# 5.5 SPECIFICATIONS OF WIFI'S BAND EANGE-REGULATORY POWERTABLE FOR US/CANADA AND EU MARKET

The power of WiFi Band eange-regulatory for **US/Canada market** as list in the table below:

| Characteristics                                 | Channel | Power (dBm) |

|-------------------------------------------------|---------|-------------|

| RF Average Output Power, 802.11b CCK Mode       | 1~11    | 16.5        |

|                                                 | 1       | 14.5        |

| RF Average Output Power, 802.11g OFDM Mode      | 2 ~ 10  | 15          |

|                                                 | 11      | 14.5        |

|                                                 | 1       | 14.5        |

| RF Average Output Power, 802.11n HT20 OFDM Mode | 2 ~ 10  | 15          |

|                                                 | 11      | 14.5        |

The power of WiFi Band eange-regulatory for **EU market** as list in the table below:

| Characteristics                                 | Channel | Power (dBm) |

|-------------------------------------------------|---------|-------------|

| RF Average Output Power, 802.11b CCK Mode       | 1~13    | 16.5        |

| RF Average Output Power, 802.11g OFDM Mode      | 1 ~ 13  | 15          |

| RF Average Output Power, 802.11n HT20 OFDM Mode | 1 ~ 13  | 15          |

#### **6 FLASH MEMORY**

#### 6.1 MCU EMBEDDED FLASH MEMORY

The STM32F205RG devices embed a 128-bit wide Flash memory of 1 Mbytes available for storing programs and data. It also features 512 bytes of OTP memory that can be used to store critical user data such as Ethernet MAC addresses or cryptographic keys.

For information on programming, erasing and protection of the internal Flash memory, please refer to the STM32F205RG Flash programming manual. The reference and Flash programming manuals are both available from the STMicroelectronics website *www.st.com*.

#### 6.2 MODULE INTERNAL MEMORY FLASH

The WM-N-BM-14 have one 8M SPI Flash in the module. This devices work voltage need 3.3V power supply. It is provide 512 bytes of OTP memory that can be used to store critical user data such as Ethernet MAC addresses or cryptographic keys. It have 86MHz speed.

For information on programming, erasing and protection of this 8M Flash memory, please refer to the Macronix MX25L8006E Flash programming manual. The reference and Flash programming manuals are both available from the Macronix website *www.macronix.com*.

#### 7 I/O PORT CHARACTERISTICS

Unless otherwise specified, the parameters given as below *Table*.

For detail information of I/O injection parameters and conditions, please refer to STM32F205RG I/O manual.

Table 7.1 I/O static characteristics

| Symbol           | Parameter                                                           | Conditions                                                         | Min                               | Тур | Max                                | Unit |  |

|------------------|---------------------------------------------------------------------|--------------------------------------------------------------------|-----------------------------------|-----|------------------------------------|------|--|

| V                | Standard IO input low<br>level voltage                              |                                                                    | -0.3                              |     | 0.28*(V <sub>DD</sub> -2 V)+0.8 V  | ٧    |  |

| V <sub>IL</sub>  | IO FT <sup>(1)</sup> input low level voltage                        |                                                                    | -0.3                              |     | 0.32*(V <sub>DD</sub> -2 V)+0.75 V | ٧    |  |

|                  | Standard IO input high<br>level voltage                             |                                                                    | 0.41*(V <sub>DD</sub> -2 V)+1.3 V |     | V <sub>DD</sub> +0.3               | ٧    |  |

| VIH              | IO FT <sup>(1)</sup> input high level                               | V <sub>DD</sub> > 2 V                                              | 0.42*/V 2.1/1.1 V                 |     | 5.5                                | · v  |  |

|                  | voltage                                                             | $V_{DD} \le 2 V$                                                   | 0.42*(V <sub>DD</sub> -2 V)+1 V   |     | 5.2                                | v    |  |

| V <sub>hys</sub> | Standard IO Schmitt<br>trigger voltage<br>hysteresis <sup>(2)</sup> |                                                                    | 200                               |     |                                    | mV   |  |

| .,,.             | IO FT Schmitt trigger<br>voltage hysteresis <sup>(2)</sup>          |                                                                    | 5% V <sub>DD</sub> <sup>(3)</sup> |     |                                    | mV   |  |

| l <sub>ikg</sub> | Input leakage current (4)                                           | V <sub>SS</sub> ≤V <sub>IN</sub> ≤V <sub>DD</sub><br>Standard I/Os |                                   |     | ±1                                 | μА   |  |

|                  |                                                                     | V <sub>IN</sub> = 5 V, I/O FT                                      |                                   |     | 3                                  |      |  |

| R <sub>PU</sub>  | Weak pull-up equivalent resistor <sup>(5)</sup>                     | V <sub>IN</sub> = V <sub>SS</sub>                                  | 30                                | 40  | 50                                 | kΩ   |  |

| R <sub>PD</sub>  | Weak pull-down<br>equivalent resistor <sup>(5)</sup>                | V <sub>IN</sub> = V <sub>DD</sub>                                  | 30                                | 40  | 50                                 | kΩ   |  |

| C <sub>IO</sub>  | I/O pin capacitance                                                 |                                                                    |                                   | 5   |                                    | pF   |  |

- 1. FT = Five-volt tolerant. In order to sustain a voltage higher than VDD+0.3 the internal pull-up/pull-down resistors must be disabled.

- 2. Hysteresis voltage between Schmitt trigger switching levels. Based on characterization, not tested in production.

- 3. With a minimum of 100 mV.

- 4. Leakage could be higher than max. if negative current is injected on adjacent pins.

- 5. Pull-up and pull-down resistors are designed with a true resistance in series with a switchable PMOS/NMOS. This MOS/NMOS contribution to the series resistance is minimum ( $\sim$ 10% order).

#### 8 COMMUNICATIONS INTERFACE

#### 8.1 I2C Interface Characteristics

The I2C bus interfaces can operate in multi-master and slave modes. They can support the Standard- and Fast-modes. The I2C characteristics are described in below Table. If need detail information, please refer to STM32F205RG I/O or Interface manual.

#### **I2C** characteristics

| Complete                                   | Parameter                               | Standard ı | node I <sup>2</sup> C <sup>(1)</sup> | Fast mode              | Unit               |      |  |

|--------------------------------------------|-----------------------------------------|------------|--------------------------------------|------------------------|--------------------|------|--|

| Symbol                                     | ranneter                                | Min        | Max                                  | Min                    | Max                | Onit |  |

| t <sub>w(SCLL)</sub>                       | SCL clock low time                      | 4.7        |                                      | 1.3                    |                    | 110  |  |

| t <sub>w(SCLH)</sub>                       | SCL clock high time                     | 4.0        |                                      | 0.6                    |                    | μs   |  |

| t <sub>su(SDA)</sub>                       | SDA setup time                          | 250        |                                      | 100                    |                    |      |  |

| t <sub>h(SDA)</sub>                        | SDA data hold time                      | 0(3)       |                                      | O <sup>(4)</sup>       | 900 <sup>(3)</sup> |      |  |

| t <sub>r(SDA)</sub><br>t <sub>r(SCL)</sub> | SDA and SCL rise time                   |            | 1000                                 | 20 + 0.1C <sub>b</sub> | 300                | ns   |  |

| t <sub>f(SDA)</sub><br>t <sub>f(SCL)</sub> | SDA and SCL fall time                   |            | 300                                  |                        | 300                |      |  |

| t <sub>h(STA)</sub>                        | Start condition hold time               | 4.0        |                                      | 0.6                    |                    |      |  |

| t <sub>su(STA)</sub>                       | Repeated Start condition setup time     | 4.7        |                                      | 0.6                    |                    | μs   |  |

| t <sub>su(STO)</sub>                       | Stop condition setup time               | 4.0        |                                      | 0.6                    |                    | μs   |  |

| t <sub>w(STO:STA)</sub>                    | Stop to Start condition time (bus free) | 4.7        |                                      | 1.3                    |                    | μs   |  |

| C <sub>b</sub>                             | Capacitive load for each bus line       |            | 400                                  |                        | 400                | pF   |  |

- 1. Guaranteed by design, not tested in production.

- 2. fPCLK1 must be higher than 2 MHz to achieve standard mode I2C frequencies. It must be higher than 4 MHz to achieve the fast mode I2C frequencies and it must be a multiple of 10 MHz in order to reach the I2C fast mode maximum clock speed of 400 kHz

- 3. The maximum hold time of the Start condition has only to be met if the interface does not stretch the low period of SCL signal.

- 4. The device must internally provide a hold time of at least 300ns for the SDA signal in order to bridge the undefined region of the falling edge of SCL.

#### 8.2 SPI / I2S interface characteristics

Unless otherwise specified, the SPI /I2S parameters are given in below Table.

Refer to STM32F205RG Datasheet: I/O port characteristics for more details on the input/output alternate function characteristics (NSS, SCK, MOSI, MISO for SPI and WS, CK, SD for I2S).

#### **SPI** characteristics

| Symbol                                               | Parameter                                                            | Conditions                                            | Min                 | Max                 | Unit    |

|------------------------------------------------------|----------------------------------------------------------------------|-------------------------------------------------------|---------------------|---------------------|---------|

| f <sub>SCK</sub>                                     | SDI alaak fraguanay                                                  | Master mode                                           | -                   | 30                  | MHz     |

| 1/t <sub>c(SCK)</sub>                                | SPI clock frequency                                                  | Slave mode                                            | -                   | 30                  | 1011 12 |

| t <sub>r(SCL)</sub><br>t <sub>f(SCL)</sub>           | SPI clock rise and fall time                                         | Capacitive load: C = 30 pF                            | -                   | 8                   | ns      |

| DuCy(SCK)                                            | SPI slave input clock duty cycle                                     | Slave mode                                            | 30                  | 70                  | %       |

| t <sub>su(NSS)</sub> <sup>(3)</sup>                  | NSS setup time                                                       | Slave mode                                            | 4 t <sub>PCLK</sub> | -                   |         |

| t <sub>h(NSS)</sub> <sup>(3)</sup>                   | NSS hold time                                                        | Slave mode                                            | 2 t <sub>PCLK</sub> | -                   |         |

| t <sub>w(SCLH)</sub> (3)<br>t <sub>w(SCLL)</sub> (3) | SCK high and low time                                                | Master mode, f <sub>PCLK</sub> = 30 MHz,<br>presc = 4 | TBD                 | TBD                 |         |

| t <sub>su(MI)</sub> (3)                              | t <sub>su(MI)</sub> (3)<br>t <sub>su(SI)</sub> Data input setup time | Master mode                                           | 5                   | -                   |         |

| t <sub>su(SI)</sub> (3)                              |                                                                      | Slave mode                                            | 5                   | -                   |         |

| t <sub>h(MI)</sub> (3)<br>t <sub>h(SI)</sub> (3)     | Data input hold time                                                 | Master mode                                           | 5                   | -                   |         |

| t <sub>h(SI)</sub> (3)                               | Data input floid time                                                | Slave mode                                            | 4                   | -                   | ns      |

| t <sub>a(SO)</sub> (3)(4)                            | Data output access time                                              | Slave mode, f <sub>PCLK</sub> = 20 MHz                | 0                   | 3 t <sub>PCLK</sub> |         |

| t <sub>dis(SO)</sub> (3)(5)                          | Data output disable time                                             | Slave mode                                            | 2                   | 10                  |         |

| t <sub>v(SO)</sub> (3)(1)                            | Data output valid time                                               | Slave mode (after enable edge)                        | -                   | 25                  |         |

| t <sub>v(MO)</sub> (3)(1)                            | Data output valid time                                               | Master mode (after enable edge)                       | -                   | 5                   |         |

| t <sub>h(SO)</sub> (3)                               | Data output hold time                                                | Slave mode (after enable edge)                        | 15                  | -                   |         |

| t <sub>h(MO)</sub> (3)                               | Data output floid tiffle                                             | Master mode (after enable edge)                       | 2                   | -                   |         |

- 1. Remapped SPI1 characteristics to be determined.

- 2. TBD stands for "to be defined".

- 3. Based on characterization, not tested in production.

- 4. Min time is for the minimum time to drive the output and the max time is for the maximum time to validate the data.

- 5. Min time is for the minimum time to invalidate the output and the max time is for the maximum time to put the data in Hi-Z

#### **I2S** characteristics

| Symbol                                                       | Parameter                                 | Conditions                                                      | Min        | Max | Unit   |

|--------------------------------------------------------------|-------------------------------------------|-----------------------------------------------------------------|------------|-----|--------|

| f <sub>CK</sub>                                              | I <sup>2</sup> S clock frequency          | Master                                                          | TBD        | TBD | MHz    |

| 1/t <sub>c(CK)</sub>                                         | 1 S clock frequency                       | Slave                                                           | 0          | TBD | IVITIZ |

| t <sub>r(CK)</sub>                                           | I <sup>2</sup> S clock rise and fall time | capacitive load<br>C <sub>L</sub> = 50 pF                       | -          | TBD |        |

| t <sub>v(WS)</sub> (2)                                       | WS valid time                             | Master                                                          | TBD        | -   |        |

| t <sub>h(WS)</sub> (2)                                       | WS hold time                              | Master                                                          | TBD        | -   |        |

| t <sub>su(WS)</sub> (2)                                      | WS setup time                             | Slave                                                           | TBD        | -   |        |

| t <sub>h(WS)</sub> (2)                                       | WS hold time                              | Slave                                                           | TBD        | -   |        |

| t <sub>w(CKH)</sub> (2)<br>t <sub>w(CKL)</sub> (2)           | CK high and low time                      | Master f <sub>PCLK</sub> = TBD,<br>presc = TBD                  | TBD        | -   |        |

| t <sub>su(SD_MR)</sub> (2)<br>t <sub>su(SD_SR)</sub> (2)     | Data input setup time                     | Master receiver<br>Slave receiver                               | TBD<br>TBD | -   |        |

| t <sub>h(SD_MR)</sub> (2)(3)<br>t <sub>h(SD_SR)</sub> (2)(3) | Data input hold time                      | Master receiver<br>Slave receiver                               | TBD<br>TBD | -   | ns     |

| t <sub>h(SD_MR)</sub> (2)<br>t <sub>h(SD_SR)</sub> (2)       | Data input hold time                      | Master f <sub>PCLK</sub> = TBD<br>Slave f <sub>PCLK</sub> = TBD | TBD<br>TBD | -   |        |

| t <sub>v(SD_ST)</sub> (2)(3)                                 | Data output valid time                    | Slave transmitter (after enable edge)                           | -          | TBD |        |

| 1(22_21)                                                     |                                           | f <sub>PCLK</sub> = TBD                                         | -          | TBD |        |

| t <sub>h(SD_ST)</sub> (2)                                    | Data output hold time                     | Slave transmitter (after enable edge)                           | TBD        | -   |        |

| t <sub>v(SD_MT)</sub> (2)(3)                                 | Data output valid time                    | Master transmitter (after enable edge)                          | -          | TBD |        |

|                                                              |                                           | f <sub>PCLK</sub> = TBD                                         | TBD        | TBD |        |

| t <sub>h(SD_MT)</sub> (2)                                    | Data output hold time                     | Master transmitter (after enable edge)                          | TBD        | -   |        |

- 1. TBD stands for "to be defined".

- 2. Based on design simulation and/or characterization results, not tested in production.

- 3. Depends on fPCLK. For example, if fPCLK=8 MHz, then TPCLK = 1/fPLCLK =125 ns.

#### 8.3 UART interface characteristics

WM-N-BM-14 Module have two universal synchronous/asynchronous receiver transmitters, USART1 and USART2. The USART1 can communicate at speeds of up to 7.5 Mbit/s. And the USAR2 interfaces communicate at up to 3.75 Mbit/s.

If need more detail information, please refer to STM32F205RG I/O or Interface manual.

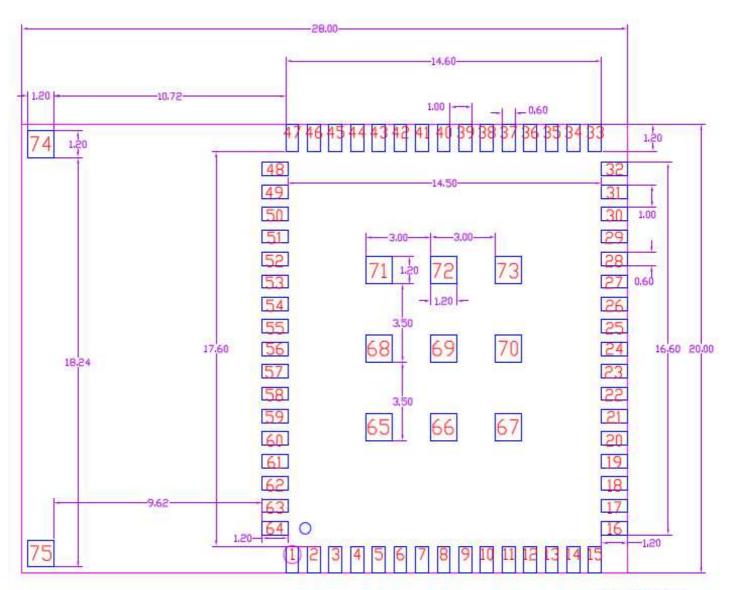

### 9 DIMENSIONS, WEIGHT AND MOUNTING

The following paragraphs provide the requirements for the size, weight and mounting of the WM-N-BM-14 module.

#### 9.1 Dimensions

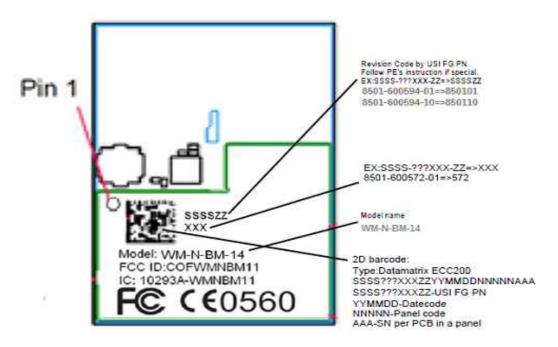

The size and thickness of the WM-N-BM-14 module is "28 mm (W) x 20 mm (L) x 2.0 mm (H)  $\pm$  0.1 mm " (Including metal shielding)

This document is controlled and confidential under the terms of USI

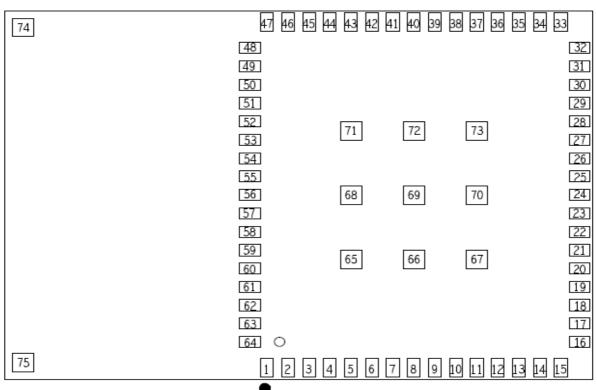

#### 9.2 Pin Out and Pin Description

#### **PIN OUT**

Top View

## Pin Description

| Pin-Number | Pin-Define   | Туре | Description                                                                       |

|------------|--------------|------|-----------------------------------------------------------------------------------|

| 1          | GND          |      | Ground                                                                            |

| 2          | VBAT_WL      | I    | Battery supply input                                                              |

| 3          | VBAT_WL      | l    | Battery supply input                                                              |

| 4          | GND          |      | Ground                                                                            |

| 5          | VDDIO_3V3_WL | I    | Digital I/O supply.                                                               |

| 6          | GND          |      | Ground                                                                            |

| 7          | WL_REG_ON    |      | WiFi reset .                                                                      |

| 8          | NC           |      |                                                                                   |

| 9          | NC           |      |                                                                                   |

| 10         | NC           |      |                                                                                   |

| 11         | NC           |      |                                                                                   |

| 12         | NC           |      |                                                                                   |

| 13         | GND          |      | Ground                                                                            |

| 14         | NC           |      |                                                                                   |

| 15         | GND          |      | Ground                                                                            |

| 16         |              |      | For normal operation, if JTAG is not used, this pin can be left unconnected (NC). |

| 10         | WL_JTAG_TDI  | I/O  | 2. This pin is also muxed UART_RX, which can be enabled by software.              |

| 17         | WL_JTAG_TCK  | ı    | For normal operation, if JTAG is not used, this pin can be left unconnected (NC). |

| 18         | WL_JTAG_TRST | 1    | For normal operation, if JTAG is not used, this pin can be left unconnected (NC). |

| 19         | WL_JTAG_TMS  | I    | For normal operation, if JTAG is not used, this pin can be left unconnected (NC). |

| 20         |              |      | For normal operation, if JTAG is not used, this pin can be left unconnected (NC). |

|            | WL_JTAG_TDO  | I/O  | 2. This pin is also muxed UART_TX, which can be enabled by software.              |

| Pin-Number | Pin-Define                | Туре | Description                                     |

|------------|---------------------------|------|-------------------------------------------------|

| 21         | MICRO_SPI1_MISO           |      | SPI1_MISO                                       |

| 22         | MICRO_SPI1_SCK            | I/O  | SPI1 CLOCK                                      |

| 23         | MICRO_SPI1_MOSI           | I/O  | SPI1_MOSI                                       |

| 24         | MICRO_SPI1_NSS            | I/O  | SPI1_NSS                                        |

| 25         | GND                       |      | Ground                                          |

| 26         | VDD_3V3                   | ı    | Power supply for I/O and the internal regulator |

| 27         | VDD_3V3                   | I    | Power supply for I/O and the internal regulator |

| 28         | GND                       |      | Ground                                          |

| 29         | MICRO_UART2_RTS           | I/O  | MICRO_UART2_RTS                                 |

| 30         | MICRO_UART2_CTS           | I/O  | MICRO_UART2_CTS                                 |

| 31         | MICRO_UART2_RXD           | I/O  | MICRO_UART2_RXD                                 |

| 32         | MICRO_UART2_TXD           | I/O  | MICRO_UART2_TXD                                 |

| 33         | TESTMODE                  | I/O  | GPIO pin                                        |

| 34         | MICRO_RST_N               | I    | MICRO reset pin                                 |

| 35         | MICRO_I2C1_SCL            | I/O  | the standard I2C communication protocol         |

| 36         | MICRO_I2C1_SDA            | I/O  | the standard I2C communication protocol         |

| 37         | GND                       |      | Ground                                          |

| 38         | VBAT_MICRO                | I    | Power supply when VDD_3V3 is not present.       |

| 39         | GND                       |      | Ground                                          |

| 40         | MICRO_GPIO1               | I/O  | GPIO pin                                        |

| 41         | MICRO_GPIO2               | I/O  | GPIO pin                                        |

| 42         | MICRO_GPIO3               | I/O  | GPIO pin                                        |

| 43         | MICRO_GPIO5               | I/O  | GPIO pin                                        |

| 44         | MICRO_GPIO6               | I/O  | GPIO pin                                        |

| 45         | MICRO_GPIO7<br>/ I2S3_SD  | I/O  | GPIO pin / also can be used on I2S3_SD          |

| 46         | MICRO_GPIO8<br>/ I2S3_MCK | I/O  | GPIO pin / also can be used on I2S3_MCK         |

| 47         | MICRO_GPIO9               | I/O  | GPIO pin                                        |

| 48         | MICRO_GPIO12              | I/O  | GPIO pin                                        |

| 49         | MICRO_GPIO13              | I/O  | GPIO pin                                        |

| Pin-Number | Pin-Define                   | Туре | Description                                                                                                                                |

|------------|------------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------|

| 50         | MICRO_GPIO14                 | I/O  | GPIO pin                                                                                                                                   |

| 51         | MICRO_JTAG_TRST              | I    | For normal operation, if JTAG is not used, this pin can be left unconnected (NC)                                                           |

| 52         | MICRO_JTAG_TDO<br>/ I2S3_SCK | I/O  | <ol> <li>For normal operation, if JTAG is not used, this pin can be left unconnected (NC)</li> <li>also can be used on I2S3_SCK</li> </ol> |

| 53         | MICRO_JTAG_TDI<br>/ I2S3_WS  | I/O  | <ol> <li>For normal operation, if JTAG is not used, this pin can be left unconnected (NC)</li> <li>also can be used on I2S3_WS</li> </ol>  |

| 54         | MICRO_JTAG_TMS               | I    | For normal operation, if JTAG is not used, this pin can be left unconnected (NC)                                                           |

| 55         | MICRO_JTAG_TCK               | I    | For normal operation, if JTAG is not used, this pin can be left unconnected (NC)                                                           |

| 56         | BTCX_STATUS                  |      | Multiplexed BT_Coex pin                                                                                                                    |

| 57         | BTCX_RF-ACTIVE               |      | Multiplexed BT_Coex pin                                                                                                                    |

| 58         | BTCX_TXCONF                  |      | Multiplexed BT_Coex pin                                                                                                                    |

| 59         | GND                          |      | Ground                                                                                                                                     |

| 60         | WL_SLEEP_CLK                 | I    | Input pin for optional high- precision 32.768kHz Clock(Sleep Clock).                                                                       |

| 61         | MICRO_UART1_RTS              | I/O  | Active-low request-to-send signal for UART interface                                                                                       |

| 62         | MICRO_UART1_CTS              | I/O  | Active-low clear-to-send signal for UART interface                                                                                         |

| 63         | MICRO_UART1_RXD              | I/O  | Serial data input for UART interface                                                                                                       |

| 64         | MICRO_UART1_TXD              | I/O  | Serial data output for UART interface                                                                                                      |

| 65 ~ 73    | GND                          |      | Ground                                                                                                                                     |

#### 10 RECOMMEND FOOTPRINT

Unit:mm

This document is controlled and confidential under the terms of USI

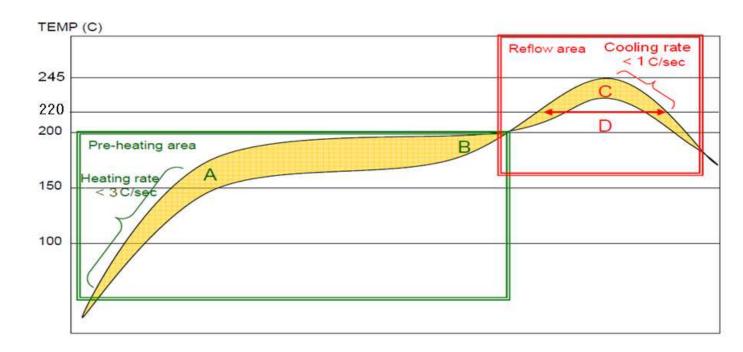

#### 11 RECOMMEND REFLOW PROFILE

A-B. Temp.: 150~200°C; soak time:60~120sec.

C. Peak temp: 235~245°C

D. Time above 220  $^{\circ}\text{C}$ : 40~90sec.

Suggestion: Optimal cooling rate is <1  $^{\circ}\text{C}$  /sec. from peak to 220  $^{\circ}\text{C}$  .

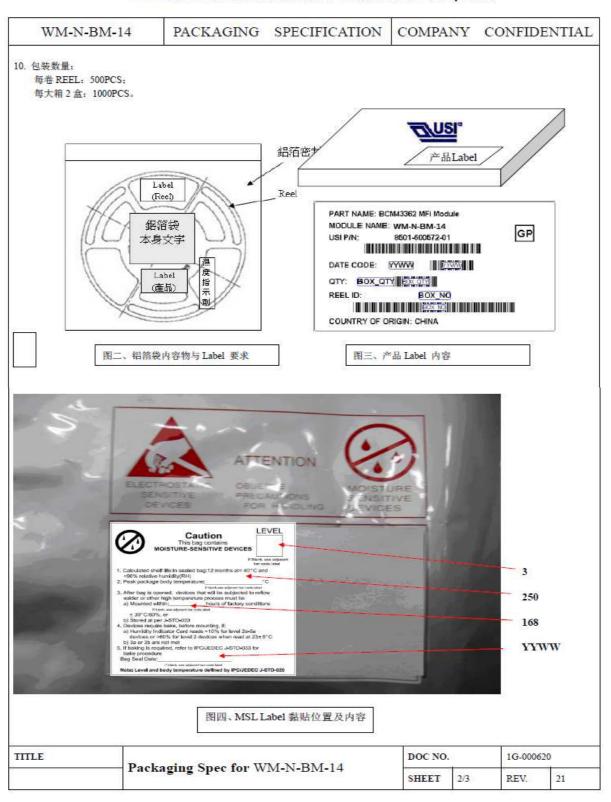

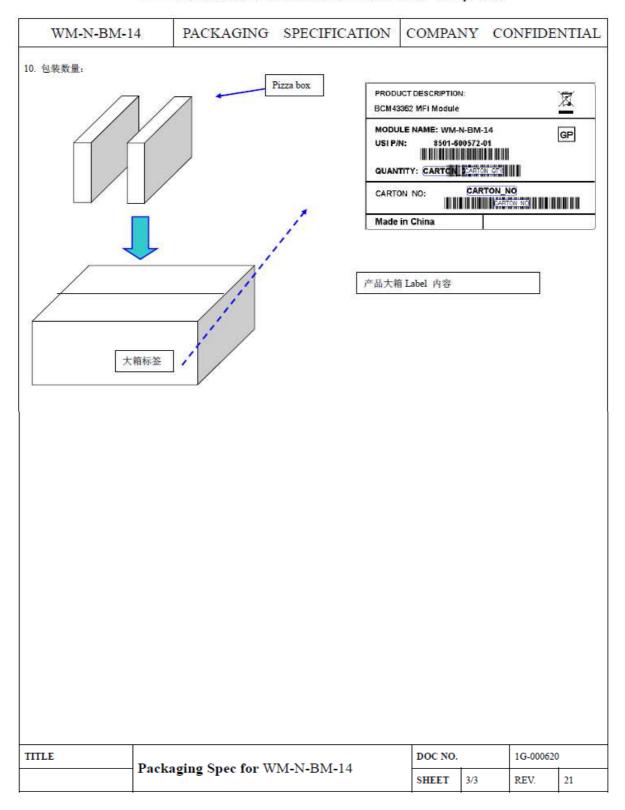

#### 12 PACKAGE AND STORAGE CONDITION

## Universal Scientific Industrial Co., Ltd.

| WM-N-BM-14 PACKAGING SPECIFICATION |          |             |                | PACKAGING SPECIFICATION |                       |           | CONFIDENTIAL         |  |                 |

|------------------------------------|----------|-------------|----------------|-------------------------|-----------------------|-----------|----------------------|--|-----------------|

| Project Name:                      | WM-N     | -BM-14      | Description: F |                         | BCM43362 WICED Module |           |                      |  |                 |

| 适用之产品:                             | 8501-600 | 594-01 / 10 | 4-01 / 10      |                         | Tape Carrier 之单元格尺寸:  |           | Tape Carrier 之单元格尺寸: |  | 97*PITCH 28(mm) |

| MSL information:                   | LEVEL:   | 3           | 3              | 温度(℃):                  | 250                   | 时间(hour): | 168                  |  |                 |

#### 使用之包装材料:

| NO | 品名                                  | P/N             | 用量(以大箱计) |

|----|-------------------------------------|-----------------|----------|

| 1  | 大 箱[360*140*360MM]                  | 59-012485-11/21 | 1        |

| 2  | Pizza 盒[340x336x40MM]               | 59-110015-02/12 | 2        |

| 3  | 产品标签(Reel/Bag/Box)                  | 59-456702-01    | 6        |

| 4  | CARRIER TAPE( 載<br>带)[80M/REEL]     | 59-308419-01    |          |

| 5  | COVER TAPE ( 透 明 带)[300M/Reel]      | 59-733786-01    |          |

| 6  | REEL(载带滚动条)                         | 59-303160-01/11 | 2        |

| 7  | Protective band(保护带)[1<br>EA=1.09m] | 59-733926-01    | 2        |

| 8  | 铝箔密封袋                               | 59-357426-11    | 2        |

| 9  | 干燥剂 (66g)(CoCl2 Free)               | 59-393005-00    | 2        |

| 10 | 大箱标签                                | 59-456703-01    | 1        |

| 11 | 湿度指示卡(CoCl2 Free)                   | 59-201004-01    | 2        |

| 12 | MSL LABEL(湿度敏感等级卷<br>标)             | 59-525934-01/11 | 2        |

#### 包装方式: (1 卷共 2000PCS)

- 1. 将 Tape Carrier、Reel、Cover Tape 装上 tape reel 包装机, CARRIER TAPE 先预留 10-13 格空格后开始放产品,每 格放 1PCS。

- 2. 包装时产品的铁盖朝上放入 carrier,定位符号朝向 carrier 定位孔(图一),每卷 REEL 装 500PCS。 3. 在 500PCS 后请预留 10-13 格空格,产品卷装后用 COVER TAPE 再多绕一圈,最后用美纹胶带固定。 4. 在卷带后,再将保护带圈于 Reel 之外围,并以美纹胶黏贴固定。

- 5. 在 REEL、铝箔袋及纸盒各贴上一张 59-456702-01(空白标签 PN: 59-514157-01)产品标签(图二)。

6. 每一铝箔密封袋放入一卷产品、一包干燥剂,及一片 6 格湿度指示卡,以真空包装机将袋口密封,如(图二)。

7. 每一个铝箔密封袋上须加贴一张 MSL 标签在 ATTENTION 旁边,填写内容如(图四)所示。

8. 将已真空包装 Reel 放入 PIZZA BOX 内,每大箱放 2 盒产品,如图五所示。

9. 大箱贴一张 59-456703-01(空白标签 PN: 59-510010-00)的大箱标签,其填写格式:

| TITLE | Packaging Spec for WM-N-BM-14 | DOC NO. | 2533 | 1G-0006 | 520 |

|-------|-------------------------------|---------|------|---------|-----|

|       | 98500 (8650 ) 1750 )          | SHEET   | 1/3  | REV.    | 21  |

## Universal Scientific Industrial Co., Ltd.

# Universal Scientific Industrial Co., Ltd.

This document is controlled and confidential under the terms of USI 27

#### 13 ESD LEVEL

#### Note:

1. Surface Resistivity:

Interior:10<sup>9</sup>~10<sup>11</sup>Ω/SQUARE EXTERIOR:10<sup>8</sup>~10<sup>12</sup>Ω/SQUARE

2. Dimension:475\*420mm

3. Tolerance:+5,0mm

4. Color:

Background: Gray

Text: Red

Length leader / trailer tape:

Leader tape: ≥550mm which includes ≥100mm of carrier tape with empty compartments and covered with tape; remaining part might be of cover tape only.

Trailer tape: ≥160mm with empty compartments and covered with tape.

#### NOTES:

- 1. Material: Conductive Polystyrene (Recycle)

- 2. Color: Black

- 3. Surface resistance: Under 10<sup>6</sup> Ohms/square.

Cumulative tolerance per 10 pictches(P<sub>0</sub>) is ±0.2mm.

A<sub>0</sub> & B<sub>0</sub> are measured on the plane by 0.3mm above the bottom of the pocket.

- 4.  $K_0$  is measured from the Inside bottom of the pocket to the top surface of the carrier.

- 5. <u>Pocket position relative to sprocket hold is measured as true position of pocket,</u> not sprocket hold.

#### 14 MSL LEVEL / STORAGE CONDITION

# CAUTION This bag contains MOISTURE-SENSITIVE DEVICES

- Calculated Shelf life in sealed bag: 12 months at < 40°C and < 90%Relative humidity (RH)</li>

- Peak package body temperature 250 °C

If Blank, see adjacent bar code label.

- After bag is opened, Devices that will be subjected to reflow solder or other high temperature process must

Mounted within: 168 hrs. Of factory conditions ≤30 ℃/60% RH, OR

If Blank, see adjacent bar code label

- (b) Stored at < 10 CRH.

- 4. Devices require bake, before mounting, it:

- (a) Humidity indicator Card is >10% when read at 23±5°C

- (b) 3a or 3b not met.

- If baking is required, Devices may be baked for 24 hrs at 125±5°C

Note: If device containers cannot be subjected to high temperature

Or shorter bake times are desired. Reference IPC/JEDEC J-STD-033 for bake procedure

Bag Seal Date: Note: Level and body temperature defined by IPC/JEDEC J-STD-020

If Blank, see adjacent bar code label

Life cycle: 2 years

For Additional information, please contact the following:

Universal Scientific Industrial Co., Ltd. Headquarters

141, Lane 351, Taiping Road, Sec. 1, Tsao-Tuen, Taiwan,

Http://www.usi.com.tw

Tel: +886-49-2350876, 2325876

Fax: +886-49-3439561, 2337360,2351093

E-mail:usi@ms.usi.com.tw